Fixing SPI Bus Crashes with W5500 + LCD

W5500과 LCD가 같은 SPI 버스를 공유하면 동시 접근으로 크래시가 날 수 있다. 재현·원인·대응(버스 분리/락/스케줄링) 가이드를 정리한다.

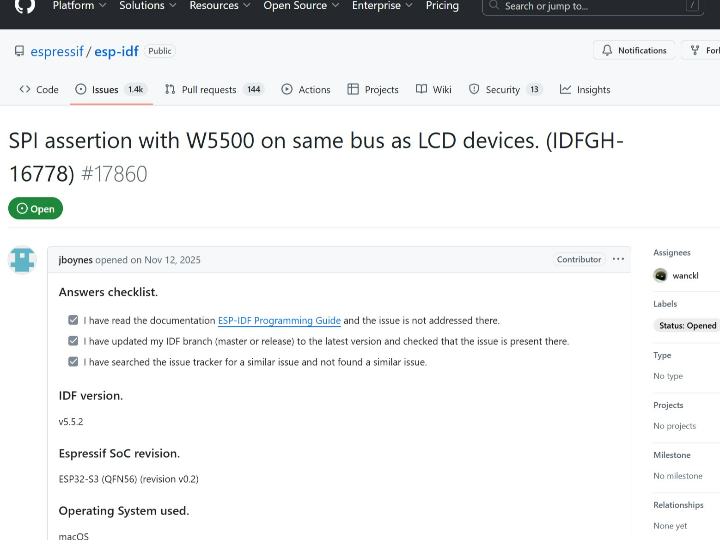

W5500 + LCD 동일 SPI 버스에서 발생하는 spi_hal_setup_trans Assert: 재현·원인·양산 설계 가이드

요약

ESP32-S3 기반 보드에서 W5500 이더넷과 LCD(LVGL)가 같은 SPI 버스를 공유할 때, 수 분 내 spi_hal_setup_trans Assert로 크래시가 발생하는 사례가 보고되었다. 이 글은 재현 조건과 증상을 정리하고, 단순 “설정 트릭”이 아니라 양산/반복 적용 가능한 구조(버스 분리, 직렬화 설계, 스케줄링, 신호 안정화)로 해결 방향을 제시한다.

1. Overview

SPI 이더넷 컨트롤러는 MCU의 부담을 줄여 주고, 안정적인 유선 네트워크를 빠르게 구현할 수 있게 해준다. 그러나 제품 설계에서 LCD/HMI 같은 고빈도 SPI 장치와 이더넷 컨트롤러를 한 버스에 함께 태우는 구성은 생각보다 자주 등장하며, 이때 동시 접근 타이밍에 따라 레이스 컨디션이 현실적인 리스크로 나타난다.

이번 사례는 “W5500 + LCD(LVGL) + 보드 지원 패키지” 조합에서, 동일 SPI 버스 공유 시 assertion이 터지는 전형적인 현장형 이슈다. 단발성 데모가 아니라, 산업용 HMI, 키오스크, PoE 기반 엣지 장치 등 ‘디스플레이 + 유선 이더넷’ 조합이 반복적으로 요구되는 시장에서 재현 가능성이 높다.

2. 증상 및 재현 조건

2.1 증상

- 동작 중(대개 수 분 이내) 시스템이 크래시

spi_hal_setup_trans관련 assert 발생- 백트레이스 경로에 W5500 SPI read 및 이더넷 태스크 처리 흐름이 포함되는 형태가 관찰됨

2.2 재현 조건(대표 패턴)

- W5500 이더넷과 LCD가 동일 SPI 버스를 공유

- LCD는 LVGL 기반으로 주기적인 화면 갱신 트래픽을 발생

- 이더넷은 링크 유지/패킷 처리로 주기적으로 SPI 접근

- 두 장치가 “각자 정상”이어도, 특정 시점의 동시성/타이밍 조합에서 문제가 재현

3. 시스템 관점에서 본 원인 가설

이 이슈는 칩 자체 결함이라기보다, 다음 구조에서 발생하는 “버스 공유 동시성 리스크”로 보는 것이 합리적이다.

- 한 개의 SPI 버스에 고빈도 장치 2개 이상이 연결됨

- 장치 A: LCD(주기적/고대역폭 갱신)

- 장치 B: W5500(주기적 네트워크 처리)

- RTOS 태스크/인터럽트 타이밍에 따라

- SPI 트랜잭션 설정/진행 상태가 기대와 달라지고,

- 드라이버 내부에서 “버스가 비어 있어야 한다”는 가정이 깨지는 순간 assert 발생

즉, “SPI 공유 자체가 문제”라기보다, 공유를 안전하게 직렬화(serialize)하는 규칙이 설계/구현에 충분히 반영되지 않았을 때 나타날 수 있는 실패 유형이다.

4. 빠른 완화(Workaround)와 한계

일부 설정(예: SPI 관련 함수의 IRAM 배치)은 타이밍을 바꿔 발생 빈도를 낮출 가능성이 있다.

하지만 양산 관점에서는 이것을 “근본 해결”로 간주하기 어렵다. 리소스 경쟁이 남아 있다면, 조건이 바뀌는 순간(디스플레이 프레임 레이트 증가, 이더넷 트래픽 증가, 다른 태스크 추가) 다시 재현될 수 있기 때문이다.

따라서 완화 설정은 임시 대응으로 두고, 아래의 구조적 해결책을 우선순위로 삼는 편이 안전하다.

5. 양산/반복 적용 가능한 해결 가이드

5.1 가장 확실한 해결: 버스 분리

가능하다면 LCD와 W5500을 서로 다른 SPI 호스트/버스로 분리하라.

- 고빈도 디스플레이 트래픽과 네트워크 트래픽을 물리적으로 분리하면, 동시성 문제의 대부분이 사라진다.

- 제품 라인업(또는 보드 리비전)에서 “버스 분리 가능한 옵션”을 남겨두면, 양산·고객사 커스텀 대응에 유리하다.

5.2 버스 공유가 필수라면: ‘직렬화 설계’를 명시적으로 넣기

버스 공유는 “된다”가 아니라, “어떻게 안전하게 공유할 것인가”를 설계 문서/코드 구조에 명시해야 한다.

- 한쪽(또는 양쪽) 드라이버가 SPI를 쥐는 구간을 뮤텍스/세마포어 등으로 확실히 직렬화

- 디스플레이 갱신과 이더넷 처리 타이밍을 스케줄링으로 분리

- 예: 화면 갱신 주기/타이밍을 조정하거나, 네트워크 처리 태스크 우선순위를 재설계

- 트랜잭션 방식(폴링/큐 기반)을 혼용할 경우 동시성 난이도가 올라가므로, 가능한 한 일관된 방식으로 통일

5.3 신호 무결성과 SPI 클럭 정책 점검

고부하 장치가 같은 버스를 공유하면 신호 품질 문제도 함께 증폭된다.

- SPI 클럭을 공격적으로 올렸다면 단계적으로 낮춰 안정성을 확인

- 배선/커넥터/실드 보드/레벨 시프터 유무에 따른 신호 품질 체크

6. W5500의 역할과 설계 포인트

W5500은 애플리케이션이 유선 네트워크를 쓰는 순간, 링크/패킷 처리 흐름을 통해 SPI 접근이 지속적으로 발생할 수 있다.

따라서 디스플레이처럼 지속적으로 SPI를 사용하는 장치와 결합되는 제품에서는 다음이 중요하다.

- “W5500 사용”은 곧 “SPI 사용량이 상시 발생할 수 있음”을 의미한다.

- LCD와 결합되는 제품에서는 **버스 리소스를 ‘공유’가 아니라 ‘관리’**하는 설계가 핵심이다.

7. 시장 확장 가능성(왜 이 글이 가치 있는가)

이 이슈는 단순 디버깅 팁이 아니라, 다음 시장에서 반복적으로 등장하는 구조를 다룬다.

- 산업용 HMI/패널: 화면 + 안정적 유선 네트워크

- 키오스크/단말기: UI + 네트워크(원격 관리/로그/업데이트)

- PoE 기반 엣지 디바이스: 설치 현장에서 전원/통신을 한 번에 해결

- 기업/ODM/OEM 프로젝트: 보드 리비전·부품 대체가 잦아 “재현 조건”이 계속 변하는 환경

즉, “한 번 해결하고 끝”이 아니라, 설계 규칙으로 만들어 두면 여러 제품/고객사에 반복 적용 가능한 자산이 된다.

8. 결론

W5500과 LCD가 동일 SPI 버스를 공유하는 구조에서 assertion 크래시가 재현될 수 있다. 임시 완화 설정이 도움이 될 수는 있지만, 양산 품질과 시장 확장성을 목표로 한다면 버스 분리 또는 명시적 직렬화 설계가 가장 안전하고 재사용 가능한 해결 방향이다.

FAQ

Q1. 이 문제가 W5500 칩 자체 문제인가요?

A. 패턴상 “버스 공유 동시성”에서 발생하는 리스크에 가깝다. 칩 결함이라기보다 설계/구현의 직렬화 규칙이 핵심이다.

Q2. 가장 추천하는 해결책은?

A. 가능하면 버스 분리. 불가하면 직렬화(락) + 스케줄링 + 트랜잭션 방식 정리.

Q3. 임시 설정만으로 양산해도 되나요?

A. 환경이 바뀌면 재현될 수 있다. 양산/ODM/OEM까지 고려하면 구조적 해결이 안전하다.

spi_hal_setup_trans Assertion with W5500 + LCD Sharing the Same SPI Bus: Reproduction, Root Cause Hypothesis, and Production-Ready Design Guide

Summary

A crash scenario has been reported on an ESP32-S3 platform where a W5500 Ethernet controller and an LCD (LVGL-based) share the same SPI bus. Within minutes, the system may fail with an assertion in spi_hal_setup_trans. This article summarizes the observable symptoms and reproduction pattern, and proposes production-ready mitigations that scale beyond a one-off demo—such as bus separation, explicit serialization, scheduling, and signal integrity practices.

1. Overview

SPI Ethernet controllers enable fast and reliable wired networking while reducing the MCU’s networking workload. In real products, however, Ethernet controllers are often paired with LCD/HMI components that also rely heavily on SPI. When both high-frequency devices share a single SPI bus, timing-dependent race conditions become a practical risk.

This case represents a typical field issue in “W5500 + LVGL LCD + board support stack” configurations. It is especially relevant for markets where “display + wired Ethernet” is a recurring requirement—industrial HMIs, kiosks, PoE edge devices, and remotely managed terminals.

2. Symptoms and Reproduction Pattern

2.1 Symptoms

- The system crashes during runtime (often within a few minutes)

- An assertion related to

spi_hal_setup_transis triggered - Backtrace patterns may include W5500 SPI read paths and Ethernet task flows

2.2 Typical Reproduction Pattern

- W5500 Ethernet and an LCD share the same SPI bus

- The LCD generates periodic, high-bandwidth SPI traffic (LVGL refresh)

- Ethernet generates periodic SPI accesses for link and packet handling

- Even if both devices work individually, certain concurrency/timing combinations trigger the failure

3. Root Cause Hypothesis from a System Perspective

This issue is more consistent with a “shared-bus concurrency risk” than a silicon defect.

- One SPI bus hosts multiple high-frequency devices

- Device A: LCD (high refresh traffic)

- Device B: W5500 (network processing traffic)

- Under RTOS scheduling and interrupt timing,

- the SPI transaction setup/execution state can deviate from driver assumptions,

- and an internal “bus must be idle” expectation may be violated, leading to the assertion

In short: the problem is not the bus sharing itself, but the absence (or insufficiency) of a robust, explicit serialization rule that guarantees safe access under load.

4. Quick Workarounds and Their Limits

Certain configuration tweaks (e.g., placing critical SPI routines in IRAM) may change timing and reduce the crash frequency.

From a production standpoint, however, such tweaks should be treated as temporary mitigations, not root fixes. As soon as conditions change—higher display frame rate, heavier Ethernet traffic, new tasks, or different board revisions—the issue can reappear.

Therefore, structural solutions should be prioritized.

5. Production-Ready Mitigation Guide

5.1 Best Fix: Separate the Buses

If possible, place the LCD and W5500 on different SPI hosts/buses.

- Physical separation eliminates most concurrency failure modes

- Keeping a “bus separation option” across product variants improves manufacturability and ODM/OEM flexibility

5.2 If Sharing Is Mandatory: Make Serialization Explicit

Bus sharing must be “managed,” not merely “allowed.”

- Enforce strict serialization using a mutex/semaphore around SPI ownership

- Separate LCD refresh and Ethernet handling via scheduling

- e.g., adjust refresh timing, revisit task priorities, avoid overlapping access peaks

- Avoid mixing transaction models (polling vs queued) unless carefully designed; consistency reduces concurrency complexity

5.3 Check Signal Integrity and SPI Clock Policy

When high-load devices share a bus, signal issues amplify.

- Validate stability by stepping down SPI clock speeds

- Review wiring length, connectors, shield boards, and level shifting paths

6. The Role of W5500 and Key Design Implications

Once the application relies on wired networking, W5500 may generate continuous SPI activity through link and packet handling.

When combined with an SPI-heavy LCD, this means:

- “Using W5500” often implies “steady SPI usage under real traffic”

- In display-enabled products, SPI is not just a connectivity path—it becomes a shared system resource that must be actively governed

7. Market Scalability (Why This Matters Beyond a Demo)

This article targets a recurring product pattern:

- Industrial HMIs/panels: display + robust wired networking

- Kiosks/terminals: UI + remote management/logging/updates

- PoE edge devices: power and connectivity solved on-site

- Enterprise/ODM/OEM deployments: frequent board revisions and component substitutions

Instead of a one-off debugging note, this can become a reusable design checklist applied across multiple products and customers.

8. Conclusion

A W5500 + LCD configuration sharing the same SPI bus can trigger a timing-dependent assertion and runtime crash. While timing tweaks may reduce frequency, production-grade robustness typically requires bus separation or explicit serialization—solutions that scale across product variants and real-world deployments.

FAQ

Q1. Is this a W5500 silicon issue?

A. The observed pattern aligns more with shared-bus concurrency design risk than a chip defect.

Q2. What is the most recommended fix?

A. Separate the buses if feasible. Otherwise, enforce strict serialization and scheduling, and align transaction models.

Q3. Can I ship with only a timing tweak?

A. It may regress under different traffic, refresh rates, or system loads. Structural mitigations are safer for production.