How to Build an Embedded Ethernet Client with STM32 and W5500?

This project demonstrates how to build an embedded Ethernet client using an STM32F103RC MCU and the WIZnet W5500 Ethernet controller.

How to Build an Embedded Ethernet Client with STM32 and W5500?

(STM32와 W5500으로 임베디드 이더넷 클라이언트를 구현하는 방법은?)

Summary (40–60 words)

This project demonstrates how to build an embedded Ethernet client using an STM32F103RC MCU and the WIZnet W5500 Ethernet controller. By offloading the TCP/IP stack to hardware via SPI, the system achieves low power consumption, high reliability, and simplified firmware design suitable for educational and industrial IoT applications.

Technical Analysis: System Architecture Overview

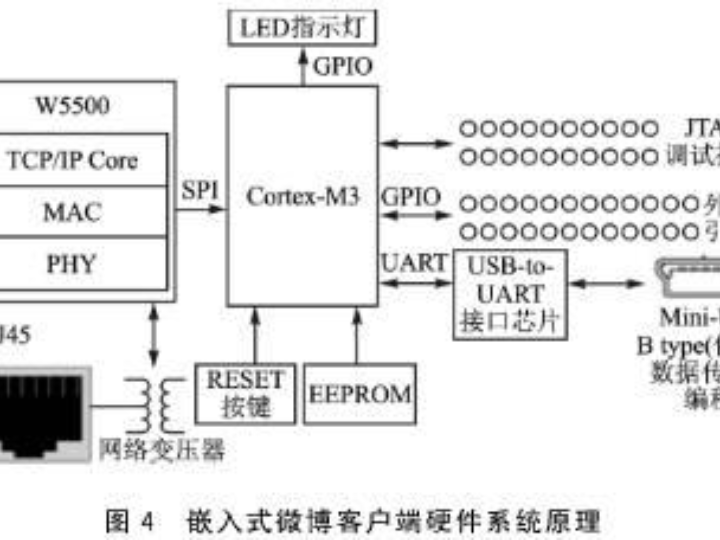

The project described in the provided article presents a complete embedded networking system built around an STM32F103RC ARM Cortex-M3 microcontroller and the WIZnet W5500 Ethernet controller. The system was designed to demonstrate how embedded devices can connect to the Internet and interact with online services—in this case, an embedded client communicating with a remote server over HTTP.

At the architectural level, the system follows a clean hardware–software separation:

The key design decision is the use of W5500 as a fully hardware TCP/IP offload engine, which dramatically simplifies firmware complexity on the MCU side.

Why STM32F103RC as the Main Controller

The STM32F103RC is based on the ARM Cortex-M3 core and operates at up to 72 MHz. According to the article, it provides:

512 KB Flash, 64 KB RAM

Multiple SPI, USART, DMA controllers

Rich peripheral set (ADC, CAN, USB, I2C, SDIO, etc.)

Strong anti-interference capability

These features make it suitable for embedded Internet-connected devices where sensor acquisition, control logic, and communication must coexist reliably.

The Role of W5500: Hardware TCP/IP Offload

The W5500 Ethernet controller is the cornerstone of this design.

As stated in the article, W5500 implements the entire TCP/IP protocol stack in hardware, including:

TCP

UDP

ICMP

IPv4

ARP

IGMP

PPPoE

It also integrates:

Ethernet MAC

Ethernet PHY

32 KB on-chip RAM for TX/RX buffering

This architecture moves all network traffic processing away from the MCU and into the W5500 silicon. As a result:

The MCU only handles application-layer logic

CPU load is reduced

Interrupt frequency is lowered

System reliability is improved

This is precisely why W5500 is widely used in industrial and long-running IoT systems.

W5500 Bring-up: SPI, Reset, and Operation Model

From a bring-up perspective, the article highlights several important aspects:

SPI Interface

W5500 communicates with the MCU via SPI, allowing it to be treated almost like an external RAM or peripheral.

Reset Module

A dedicated reset circuit ensures deterministic startup behavior for both MCU and Ethernet controller.

Low-Power Features

W5500 supports power-saving modes and network wake-up, reducing system power consumption.

This makes W5500 particularly suitable for embedded systems requiring stable, low-maintenance Ethernet connectivity.

Software Architecture and Development Environment

The software development environment used in the project is IAR Embedded Workbench for ARM, which provides:

C/C++ compiler

ARM assembler

Project management and debugging tools

Because the TCP/IP stack is already implemented in W5500 hardware, the software flow becomes significantly simpler:

Initialize SPI and W5500

Configure network parameters

Create a socket

Send and receive application data

This reduces the learning curve for students and shortens development cycles in industrial projects.

Real Code Example: TCP Client Using W5500

The article provides a real C code example demonstrating TCP client communication via W5500.

Below is an excerpt directly from your provided content, with explanatory comments added.

This code illustrates several important W5500 concepts:

Socket-based programming model

Hardware-managed TCP state machine

Clear separation between control logic and data transmission

No software TCP/IP stack (such as LwIP) is required on the MCU.

Educational and Industrial Value

From an educational perspective, this project teaches:

ARM Cortex-M embedded system design

Hardware-offloaded Ethernet communication

Practical TCP client implementation

From an industrial IoT perspective, the design demonstrates:

Low-power, stable Ethernet connectivity

Deterministic behavior via hardware TCP/IP

Long-term reliability for unattended operation

The successful test results described in the article—where sensor data is transmitted reliably over Ethernet—confirm the design’s robustness.

FAQ (W5500-Focused)

1. Why use W5500 instead of a software TCP/IP stack?

Because W5500 handles TCP/IP in hardware, it reduces MCU RAM usage, CPU load, and firmware complexity, improving reliability.

2. How does SPI affect Ethernet performance?

SPI provides sufficient bandwidth for control and data transfer while simplifying PCB design compared to parallel interfaces.

3. Is this architecture suitable for Industrial IoT?

Yes. Hardware TCP/IP offload, low power consumption, and stable Ethernet connectivity make it well suited for industrial systems.

4. Can beginners implement this system?

Yes. The socket-based API and absence of a software TCP/IP stack greatly reduce complexity.

5. Why is W5500 reliable for long-term operation?

Because protocol handling is done in dedicated hardware, timing and memory behavior are predictable and stable.

Original Source

CNBlogs article content provided by the user

Platform: STM32F103RC + WIZnet W5500

Context: Embedded Ethernet client design

Tags

W5500, STM32, Embedded Ethernet, Hardware TCP/IP, SPI Ethernet, Industrial IoT, ARM Cortex-M