Why Do SPI Multi-Byte Access and CS Timing Matter for Stable TCP on W5500?

This article explains how correct SPI multi-byte access, register read/write patterns, and chip-select timing directly affect TCP stability on the WIZnet W5500.

Why Do SPI Multi-Byte Access and CS Timing Matter for Stable TCP on W5500?

(SPI 다중 바이트 접근과 CS 타이밍은 W5500 TCP 안정성에 왜 중요한가?)

Summary (40–60 words)

This article explains how correct SPI multi-byte access, register read/write patterns, and chip-select timing directly affect TCP stability on the WIZnet W5500. By analyzing common driver-level mistakes and failure modes, it shows how a deterministic SPI and buffer model enables reliable, portable Ethernet firmware suitable for long-running and industrial systems.

1. Why TCP Problems Often Start Below the TCP Layer

When TCP communication fails on embedded Ethernet systems, developers often suspect:

Socket state machines

Server behavior

Network instability

However, in W5500-based systems, most TCP failures originate at the driver level, specifically in:

SPI transaction framing

Multi-byte register access

TX/RX buffer pointer handling

Because W5500 implements TCP/IP in hardware, software errors usually come from incorrect register and buffer access, not from TCP logic itself.

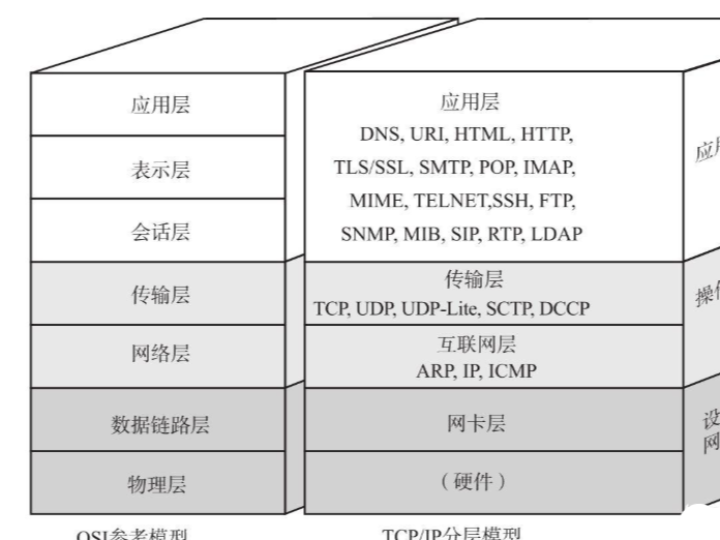

2. W5500 Driver-Level Architecture (Big Picture)

Logical Architecture

Key point:

TCP reliability depends on deterministic SPI transactions.

3. Register and Buffer Model: Why Multi-Byte Access Exists

W5500 exposes:

16-bit register addresses

16-bit TX/RX buffer pointers

Variable-length data regions

This naturally requires multi-byte SPI access.

Typical Multi-Byte Operations

Writing socket TX write pointer (2 bytes)

Reading RX received size (2 bytes)

Writing application payload (N bytes)

Reading received TCP stream data (N bytes)

These operations must be atomic from the W5500’s perspective.

4. SPI Multi-Byte Access: Correct vs Incorrect Patterns

Correct Conceptual Pattern

This ensures:

Continuous address auto-increment

Correct buffer pointer movement

Valid TCP payload framing

Common Incorrect Pattern (Bug Source)

This breaks:

Address continuity

Buffer pointer synchronization

TCP stream integrity

Resulting symptoms:

TCP connect succeeds, but send fails

Data appears corrupted

Socket resets unexpectedly

5. CS Timing: Why “Almost Correct” Is Still Wrong

W5500 SPI supports Variable Length Data Mode (VDM), where:

CS LOW duration defines the transaction boundary

This means:

CS toggled too early → truncated operation

CS toggled between bytes → undefined behavior

CS controlled outside the driver → race conditions

Deterministic Rule

One logical register or buffer operation = one CS LOW window

Anything else introduces non-determinism.

6. TX/RX Buffer Access and Pointer Consistency

Why Buffer Pointers Matter

TCP on W5500 relies on:

TX write pointer

TX read pointer

RX write pointer

RX read pointer

If multi-byte access is broken:

Pointers desynchronize

TCP hardware sends invalid segments

RX data appears shifted or duplicated

Conceptual Safe Flow

Breaking any step across CS boundaries causes instability.

7. TCP Socket Lifecycle Depends on Driver Correctness

Hardware TCP States (Simplified)

W5500 handles these states internally.

The driver’s responsibility is only to:

Write correct registers

Move data correctly

If SPI access is flawed:

Socket may never reach ESTABLISHED

SEND command silently fails

Socket resets without error flags

This is why driver correctness appears as “TCP instability.”

8. Common Driver-Level Mistakes and Their Symptoms

| Mistake | Symptom | Root Cause |

|---|---|---|

| Split CS during multi-byte write | Corrupted TCP payload | Broken auto-increment |

| Byte-wise SPI writes | Random send failure | Pointer mismatch |

| CS controlled in application | Race condition | Non-atomic SPI |

| Ignoring RX size alignment | Partial reads | Stream desync |

Understanding multi-byte access eliminates these issues.

9. Why Deterministic SPI + Buffer Model Enables Stability

When SPI access is:

Atomic

Predictable

Driver-controlled

Then:

TCP behavior becomes repeatable

Bugs become reproducible

Firmware becomes portable across MCUs and RTOSes

This is why W5500 is widely used in industrial and long-running systems.

10. Key Takeaway for Driver Developers

On W5500, TCP stability is a direct result of correct SPI multi-byte access and CS discipline.

Once the driver layer is deterministic:

TCP “just works”

Higher-level logic becomes trivial

Debugging effort drops dramatically

FAQ (Driver-Level Focus)

Q1. Is byte-by-byte SPI access safe?

No. It breaks pointer continuity and must be avoided.

Q2. Can CS be toggled between bytes?

No. One logical operation requires one CS window.

Q3. Does this apply to UDP as well?

Yes, but TCP is more sensitive to pointer errors.

Q4. Is this RTOS-specific?

No. This applies to bare-metal and RTOS systems alike.

Q5. Why does this matter for Industrial IoT?

Because deterministic behavior is more important than peak speed.

Source

CNBlogs driver-level W5500 SPI/register discussion

WIZnet W5500 datasheet (SPI & memory architecture)

Tags

W5500, WIZnet, SPI Ethernet, Multi-byte Access, CS Timing, TCP Driver, Embedded Ethernet, Industrial IoT, Debugging Guide

🇰🇷 한국어 번역 (1:1 Full Translation)

SPI 다중 바이트 접근과 CS 타이밍은 W5500 TCP 안정성에 왜 중요한가?

요약

본 문서는 WIZnet W5500에서 SPI 다중 바이트 접근, 레지스터 읽기/쓰기 패턴, CS 타이밍이 TCP 통신 안정성에 어떤 영향을 미치는지를 설명한다. 드라이버 수준의 일반적인 오류와 실패 사례를 분석하여, 결정적인 SPI 및 버퍼 모델이 왜 산업용 이더넷 시스템에 중요한지를 보여준다.

1. TCP 문제는 왜 TCP 계층에서 시작되지 않는가

W5500은 TCP/IP를 하드웨어로 처리한다.

따라서 대부분의 문제는:

SPI 접근 오류

버퍼 포인터 불일치

CS 타이밍 위반

에서 발생한다.

2. W5500 드라이버 구조 개요

TCP 안정성 = SPI 결정성.

3. 다중 바이트 접근이 필요한 이유

16비트 주소

16비트 포인터

연속 데이터 스트림

모두 원자적 접근이 필요하다.

4. 올바른 SPI 다중 바이트 패턴

CS 분리는 허용되지 않는다.

5. CS 타이밍의 중요성

VDM 모드에서 CS는 트랜잭션 경계다.

중간에 CS를 올리면 동작은 정의되지 않는다.

6. TX/RX 버퍼와 포인터 일관성

포인터 오류는 TCP 스트림 붕괴로 이어진다.

7. TCP 소켓 생명주기와 드라이버

소켓 상태 오류는 대부분 드라이버 오류다.

8. 자주 발생하는 실수

| 실수 | 결과 |

|---|---|

| CS 분리 | 데이터 손상 |

| 바이트 단위 접근 | 랜덤 실패 |

| 응용단 CS 제어 | 레이스 조건 |

9. 결정적 SPI 모델의 가치

재현 가능성

이식성

장기 안정성

10. 핵심 메시지

W5500에서 TCP 안정성은 SPI 다중 바이트 접근과 CS 규율에서 나온다.

태그

W5500, WIZnet, SPI 다중 바이트, CS 타이밍, TCP 드라이버, 임베디드 이더넷, 산업용 IoT