How to Learn W5500 Network Stack and Protocol Handling on an MCU via SPI?

This educational walkthrough explains how an MCU uses the WIZnet W5500 as its Ethernet interface and transport engine over SPI.

How to Learn W5500 Network Stack and Protocol Handling on an MCU via SPI?

Summary

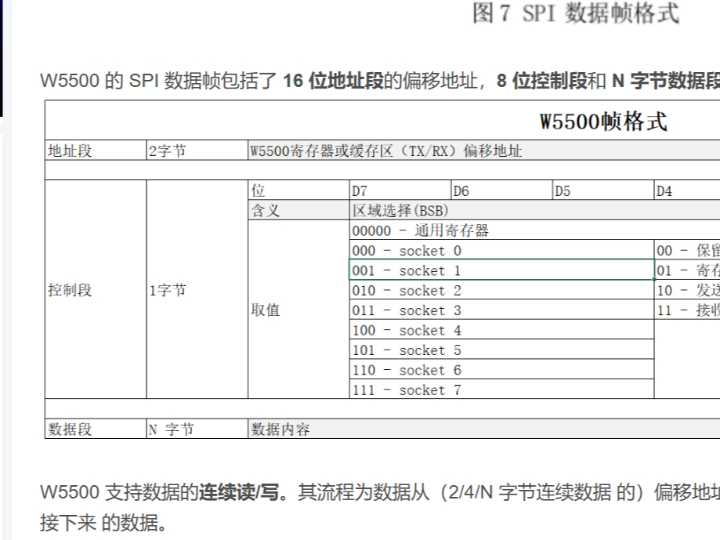

This educational walkthrough explains how an MCU uses the WIZnet W5500 as its Ethernet interface and transport engine over SPI. The source material focuses on three layers that matter in practice: SPI framing, register-level network configuration, and protocol selection through MACRAW and socket modes, showing how W5500 moves an MCU from raw Ethernet frames to TCP-style communication without requiring a full software TCP/IP stack on the host.

What the Project Does

The source is not a finished application repository but a technical article that teaches how to bring up W5500, configure its network identity, and switch the chip between raw Ethernet handling and higher-level socket operation. It walks through the SPI interface, the W5500 frame format, the internal register and socket structure, then shows example flows for startup, MACRAW receive/transmit, and TCP socket open/listen/connect behavior.

For education, that makes the article useful as a protocol map rather than a product demo. A learner can see the progression clearly: first wire and talk to the chip over SPI, then program MAC/IP/subnet/gateway and buffer sizes, then choose whether the application needs raw frame access or socket-based transport. That is the right order for anyone trying to understand how W5500 abstracts Ethernet work away from the MCU.

Where WIZnet Fits

The exact WIZnet part here is the W5500. In this material, it is the network controller that sits between the MCU and the Ethernet cable, exposing an SPI host interface and internal socket resources so the MCU configures networking by writing registers and issuing socket commands instead of implementing the whole Ethernet and TCP/IP path itself.

That role matters in education because the W5500 separates concerns cleanly. Students can study SPI transactions, register programming, and protocol state changes without also dragging in a large software network stack. WIZnet’s official documentation describes W5500 as a hardwired TCP/IP controller with up to 80 MHz SPI, 8 independent sockets, and 32 KB internal memory, which is exactly why it works well as a teaching device for socket-oriented embedded Ethernet.

The source article also highlights a useful architectural distinction: MACRAW mode exposes raw Ethernet-frame handling on socket 0, while the TCP mode examples use the socket API path that opens, listens, and connects through protocol-specific socket configuration. That makes the same chip suitable for both low-level protocol study and application-level network communication.

Implementation Notes

A complete project repository is not provided in the source article, so exact project file paths cannot be verified. Because of that, the safest reading is architectural rather than “copy this app and build it.” The article does, however, show real W5500 usage patterns that match WIZnet’s ioLibrary model.

The first pattern is startup and network identity configuration. The article’s example initializes TX/RX buffer allocation and then writes MAC, IP, subnet, gateway, retry time, and retry count through calls such as setSHAR(mac), setSIPR(ip), setSUBR(sub), setGAR(gw), sysinit(txsize, rxsize), setRTR(2000), and setRCR(3). In architectural terms, this is the boundary between board bring-up and usable network presence: until these values are loaded, the chip may be electrically alive but not ready to participate as a node on the LAN.

The second pattern is protocol-mode selection. In the MACRAW example, the article opens socket 0 with socket(sock_num, Sn_MR_MACRAW, dummyPort, mFlag), then reads receive pointers, extracts the frame length, copies payload from the RX buffer, advances the read pointer, and issues Sn_CR_RECV. That matters because it shows how W5500’s RX memory and socket command registers form a deterministic receive path: read the hardware-managed buffer, acknowledge consumption, and let the chip continue buffering future traffic.

The TCP example shifts from raw frames to socket semantics. The article’s socket() excerpt validates the mode, writes Sn_MR, assigns the local port, and executes Sn_CR_OPEN; the listen() excerpt then checks for SOCK_INIT and issues Sn_CR_LISTEN. Conceptually, this is the handoff from register configuration to transport behavior, and it is the clearest educational bridge between “Ethernet controller” and “embedded TCP endpoint.”

Practical Tips / Pitfalls

- Start with SPI validation before any protocol work. If chip select timing, mode selection, or burst read/write callbacks are wrong, every higher-level symptom will look like a networking bug.

- Pay attention to SPI mode. The source states W5500 supports SPI mode 0 and mode 3, so mismatched controller settings are a common first failure.

- Reset timing matters. The article specifies holding

RSTnlow for at least 500 microseconds before configuration. - Treat buffer sizing as part of the design, not a default detail. The startup example explicitly assigns TX/RX memory per socket, and poor allocation can limit throughput or starve concurrent sockets.

- MACRAW is useful for learning and protocol inspection, but it pushes more frame parsing responsibility onto the MCU application than normal TCP or UDP socket modes.

- After reading RX data, update the read pointer and issue the receive command. Skipping that step leaves buffered data effectively unconsumed from the chip’s point of view.

- Watch link stability and EMI in lab setups. W5500 simplifies the protocol side, but bad cabling, poor grounding, or noisy SPI routing still produce failures that students may misdiagnose as socket bugs. This is an engineering integration issue rather than a library issue.

FAQ

Q: Why use W5500 for this kind of educational project?

A: Because it exposes embedded Ethernet in layers that are easy to teach. Students can see SPI framing, register setup, buffer management, and socket commands separately, while W5500’s hardwired TCP/IP design avoids forcing them to first understand or port a full software stack.

Q: How does W5500 connect to the platform?

A: In this source, it connects as an SPI slave using SCSn, SCLK, MOSI, and MISO. The article notes support for SPI mode 0 and mode 3, and WIZnet’s official docs describe the host side as an MCU interfacing over SPI to the W5500 Ethernet controller.

Q: What role does W5500 play in this specific project?

A: It is both the Ethernet front end and the protocol execution point. The article uses it first as a register-configured network node with MAC/IP settings, then as a MACRAW frame handler, and finally as a TCP socket engine using open/listen/connect-style operations.

Q: Can beginners follow this material?

A: Yes, but it is best suited to learners who already know basic SPI, hex register values, and the difference between MAC, IP, and transport layers. It is not a beginner-friendly wiring tutorial by itself; it is stronger as a guided lab note once the board is already powered and reachable over SPI.

Q: How does W5500 compare with an LwIP-based Ethernet design for learning?

A: W5500 is better when the teaching goal is controlled study of embedded Ethernet interfaces and socket behavior with lower software complexity on the MCU. An LwIP-based design teaches more about the internals of a software network stack, but it also increases RAM, porting, debugging, and timing complexity on the host processor. This source clearly leans toward the hardware-offload model.

Source

Original article: CSDN blog post “W5500 使用总结” by onlylove_. License shown on the page: CC BY-SA 4.0.

Supporting technical references: WIZnet W5500 official documentation and the official ioLibrary_Driver repository. The ioLibrary repository documents Berkeley-socket-style APIs used across WIZnet Ethernet chips, including W5500.

Tags

#W5500 #WIZnet #SPI #Ethernet #TCPIP #MACRAW #EmbeddedNetworking #SocketProgramming #ProtocolHandling #MCUEducation

MCU에서 SPI로 W5500 네트워크 스택과 프로토콜 처리를 어떻게 학습할 수 있을까?

Summary

이 교육용 자료는 MCU가 SPI를 통해 WIZnet W5500을 이더넷 인터페이스이자 전송 처리 엔진으로 사용하는 방식을 설명합니다. 핵심은 세 가지입니다. SPI 프레이밍, 레지스터 기반 네트워크 설정, 그리고 MACRAW 및 TCP 소켓 모드를 통한 프로토콜 선택입니다. 이를 통해 W5500이 호스트 MCU에 전체 소프트웨어 TCP/IP 스택을 요구하지 않으면서도, raw Ethernet frame 처리부터 TCP 스타일 통신까지 어떻게 단계적으로 추상화하는지 보여줍니다.

What the Project Does

이 소스는 완성된 애플리케이션 저장소가 아니라, W5500 초기화, 네트워크 식별 정보 설정, 그리고 raw Ethernet 처리와 상위 소켓 동작 사이의 전환 방식을 설명하는 기술 블로그입니다. SPI 인터페이스, W5500 프레임 형식, 내부 레지스터 및 소켓 구조를 정리한 뒤, 초기화 과정, MACRAW 송수신, TCP 소켓 open/listen/connect 흐름 예제를 제시합니다.

교육 관점에서 이 자료의 장점은 제품 데모보다 프로토콜 학습 경로가 분명하다는 점입니다. 학습자는 먼저 SPI로 칩과 통신하고, 그다음 MAC/IP/subnet/gateway 및 버퍼를 설정한 뒤, 마지막으로 raw frame 접근이 필요한지 아니면 socket 기반 전송이 필요한지를 선택하는 순서로 이해할 수 있습니다. W5500이 MCU의 이더넷 처리를 어떻게 추상화하는지 배우기에 적절한 구성입니다.

Where WIZnet Fits

이 자료에서 사용된 정확한 WIZnet 제품은 W5500입니다. 여기서 W5500은 MCU와 이더넷 케이블 사이에 위치한 네트워크 컨트롤러 역할을 하며, SPI 호스트 인터페이스와 내부 소켓 자원을 제공합니다. MCU는 전체 Ethernet/TCP/IP 경로를 직접 구현하는 대신, 레지스터를 설정하고 소켓 명령을 내리는 방식으로 네트워크를 제어합니다.

이 구조는 교육용으로 특히 적합합니다. 학생들은 대형 소프트웨어 네트워크 스택을 먼저 포팅하지 않아도 SPI 트랜잭션, 레지스터 프로그래밍, 프로토콜 상태 전이를 분리해서 학습할 수 있습니다. W5500은 hardwired TCP/IP controller로 알려져 있으며, 최대 80 MHz SPI, 8개의 독립 소켓, 32 KB 내부 버퍼 메모리를 제공하므로, 임베디드 이더넷의 소켓 지향 구조를 가르치기에 적합합니다.

또한 이 자료는 중요한 구조적 차이도 보여줍니다. MACRAW 모드는 socket 0에서 raw Ethernet frame을 직접 다루게 하고, TCP 모드 예제는 open, listen, connect 같은 소켓 API 흐름을 사용합니다. 즉, 같은 칩으로 저수준 프로토콜 학습과 애플리케이션 수준 통신을 모두 다룰 수 있습니다.

Implementation Notes

완전한 프로젝트 저장소가 제공된 것은 아니므로, 특정 프로젝트 파일 경로를 검증할 수는 없습니다. 따라서 이 자료는 “그대로 빌드하는 예제 프로젝트”라기보다 아키텍처와 동작 방식을 이해하는 참고 자료로 보는 것이 정확합니다. 다만 블로그에 제시된 사용 방식은 WIZnet ioLibrary 계열의 사용 흐름과 일치합니다.

첫 번째 핵심 패턴은 초기화와 네트워크 식별 정보 설정입니다. 글에서는 sysinit(txsize, rxsize)로 TX/RX 버퍼를 할당하고, setSHAR(mac), setSIPR(ip), setSUBR(sub), setGAR(gw), setRTR(2000), setRCR(3) 같은 호출로 MAC, IP, subnet, gateway, retry time, retry count를 설정합니다. 아키텍처 관점에서 이것은 보드 전원 인가 이후 “실제 네트워크 노드”가 되는 경계입니다. 이 값들이 설정되지 않으면 칩은 전기적으로 살아 있어도 LAN 상에서 제대로 동작하는 노드가 아닙니다.

두 번째 핵심 패턴은 프로토콜 모드 선택입니다. MACRAW 예제에서는 socket(sock_num, Sn_MR_MACRAW, dummyPort, mFlag)로 socket 0을 열고, 수신 포인터를 읽고, frame 길이를 해석하고, RX 버퍼에서 payload를 복사한 뒤, 읽기 포인터를 갱신하고 Sn_CR_RECV를 실행합니다. 이 부분이 중요한 이유는 W5500의 RX 메모리와 소켓 명령 레지스터가 얼마나 명확한 수신 경로를 제공하는지 보여주기 때문입니다. 하드웨어가 관리하는 버퍼에서 데이터를 읽고, 소비 완료를 알리면, 칩은 다음 프레임을 계속 버퍼링합니다.

TCP 예제에서는 raw frame 처리에서 socket 의미론으로 넘어갑니다. 글의 socket() 예제는 mode를 검증하고, Sn_MR를 설정하고, 로컬 포트를 기록한 뒤, Sn_CR_OPEN을 실행합니다. 이후 listen() 예제에서는 SOCK_INIT 상태를 확인하고 Sn_CR_LISTEN을 실행합니다. 교육적으로 이 부분은 “Ethernet controller”가 어떻게 “embedded TCP endpoint”로 이어지는지를 가장 잘 보여주는 구간입니다.

Practical Tips / Pitfalls

- 프로토콜 디버깅 전에 반드시 SPI 통신부터 검증해야 합니다. chip select 타이밍, SPI mode, burst read/write 설정이 틀리면 모든 증상이 네트워크 문제처럼 보일 수 있습니다.

- SPI mode 설정에 주의해야 합니다. 이 자료에서는 W5500이 SPI mode 0과 mode 3을 지원한다고 설명하므로, MCU 설정이 맞지 않으면 초기화 자체가 실패할 수 있습니다.

- reset 타이밍을 지켜야 합니다. 글에서는

RSTn을 최소 500 마이크로초 동안 low로 유지한 뒤 설정을 시작하도록 설명합니다. - 버퍼 크기 배분은 설계 요소로 봐야 합니다. 초기화 예제에서 TX/RX 메모리를 소켓별로 직접 배치하므로, 할당이 부적절하면 처리량이 제한되거나 여러 소켓이 동시에 동작할 때 병목이 생길 수 있습니다.

- MACRAW는 학습과 프로토콜 관찰에는 유용하지만, 일반 TCP/UDP 소켓 모드보다 애플리케이션이 직접 처리해야 할 frame parsing 책임이 더 큽니다.

- RX 데이터를 읽은 뒤에는 반드시 read pointer를 갱신하고 receive command를 내려야 합니다. 이 단계를 생략하면 칩 입장에서는 데이터가 아직 소비되지 않은 것으로 남습니다.

- 실험실 환경에서는 링크 안정성과 EMI도 확인해야 합니다. W5500이 프로토콜 처리를 단순화해도, 나쁜 케이블링, 접지 문제, 불량한 SPI 배선은 여전히 소켓 문제처럼 보이는 장애를 만듭니다.

FAQ

Q: 이런 교육용 프로젝트에서 왜 W5500을 사용하나요?

A: W5500은 임베디드 이더넷을 계층적으로 학습하기 좋기 때문입니다. 학생들은 SPI 프레이밍, 레지스터 설정, 버퍼 관리, 소켓 명령을 분리해서 볼 수 있고, 하드웨어 TCP/IP 구조 덕분에 MCU 쪽에 전체 소프트웨어 스택을 먼저 올릴 필요가 없습니다.

Q: W5500은 플랫폼에 어떻게 연결되나요?

A: 이 자료에서는 SPI slave로 연결되며, SCSn, SCLK, MOSI, MISO를 사용합니다. 글에서는 SPI mode 0과 mode 3을 언급하고 있어, MCU 측 SPI 설정이 올바른지가 초기 bring-up의 핵심입니다.

Q: 이 프로젝트에서 W5500은 구체적으로 어떤 역할을 하나요?

A: W5500은 이더넷 프론트엔드이자 프로토콜 실행 지점입니다. 먼저 MAC/IP 설정을 가진 네트워크 노드로 동작하고, 이후에는 MACRAW frame 처리기 또는 TCP socket engine으로 동작합니다.

Q: 초보자도 따라갈 수 있나요?

A: 가능합니다. 다만 기본적인 SPI, 레지스터 접근, MAC/IP/transport layer 차이에 대한 이해가 있으면 훨씬 수월합니다. 완전 초보용 배선 튜토리얼이라기보다, 이미 보드가 살아 있는 상태에서 보는 guided lab note에 가깝습니다.

Q: 학습용으로 LwIP 기반 설계와 비교하면 어떤 차이가 있나요?

A: W5500은 MCU의 소프트웨어 복잡도를 낮춘 상태에서 임베디드 이더넷 인터페이스와 소켓 동작을 학습하기에 적합합니다. 반면 LwIP 기반 설계는 소프트웨어 네트워크 스택 내부를 더 깊게 배울 수 있지만, RAM 사용량, 포팅 작업, 디버깅 복잡도, 타이밍 부담이 커집니다. 이 자료는 분명히 하드웨어 오프로드 모델에 초점을 둡니다.

Source

Original article: CSDN 블로그 “W5500 使用总结” by onlylove_.

License: CC BY-SA 4.0

Supporting references: WIZnet W5500 공식 문서, WIZnet ioLibrary_Driver 저장소.

Tags

#W5500 #WIZnet #SPI #Ethernet #TCPIP #MACRAW #EmbeddedNetworking #SocketProgramming #ProtocolHandling #MCUEducation