riocore

riocore

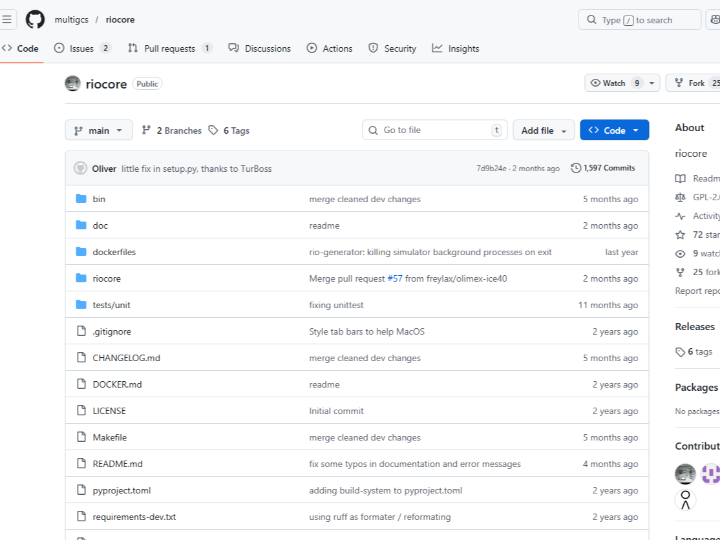

🚀 RioCore: Open-Source FPGA Real-Time IO

RioCore is a high-performance, open-source project designed to bring industrial-grade real-time control to everyone. Created by Oliver Dippel (multigcs), it bridges the gap between affordable FPGA hardware and professional motion control systems like LinuxCNC.

📝 Project Overview

RioCore serves as a Real-Time IO (RIO) system that eliminates the need for expensive proprietary hardware. It isn't just a piece of firmware; it’s a Hardware Generation Platform. By using a Python-based configurator, users can generate custom FPGA logic (Verilog) tailored to their specific machine requirements without writing a single line of HDL code.

✨ Why RioCore? Key Features & Benefits

Zero Jitter Performance: Unlike software-based IO, RioCore runs on pure hardware logic. This ensures nanosecond-precision timing, which is critical for high-speed motor synchronization.

Massive Cost Savings: Instead of spending hundreds of dollars on industrial cards (like Mesa boards), you can achieve the same—or better—results using budget-friendly FPGAs (Tang Nano, iCE40, ECP5).

Automated Code Generation: The rio-generator handles the heavy lifting, automatically creating the FPGA bitstream and the necessary LinuxCNC configuration files (HAL/INI).

Modular Plugin System: Need more PWM? Extra encoders? A UART bridge? Just add the plugin in the GUI, and the system reconfigures itself.

🔌 The Role of WIZnet W5500: The Network Powerhouse

In the RioCore architecture, the WIZnet W5500 is the essential "Bridge" between the PC and the FPGA.

Hardwired TCP/IP Stack: Implementing a full Ethernet stack inside an FPGA consumes massive amounts of logic gates. The W5500 handles all TCP/IP processing internally, freeing up the FPGA's resources for what it does best: precision motion control.

UDP Communication Bridge: It receives high-speed UDP packets from the host PC and translates them into SPI data that the FPGA can process instantly.

Reliable Latency: By offloading the network stack to hardware, the W5500 maintains an incredibly stable 1ms (or faster) servo loop, which is the gold standard for CNC reliability.

🛠 Hardware Configuration & Analysis

https://github.com/multigcs/riocore/blob/main/riocore/boards/README.md

RioCore is designed for flexibility, supporting a wide range of hardware combinations:

FPGA Gateware: Built using Verilog, optimized for low resource usage so it can fit on small FPGAs like the Gowin Tang Nano 9K.

Host Interface: Supports either SPI (for direct connection to a Raspberry Pi) or Ethernet via W5500 (for standard PC setups).

Architecture Analysis: The beauty of RioCore lies in its Abstraction. The Python generator takes high-level user requirements and maps them directly to FPGA pins and internal registers, creating a seamless "Software-to-Silicon" pipeline.

🛠 Technical Deep Dive: The Engineering Behind RioCore

What makes RioCore stand out isn't just its functionality, but the elegant way it handles high-speed data and hardware logic. Let’s look at the four architectural pillars found within its Verilog code.

1. Register-Mapped Architecture

RioCore treats the entire FPGA internal logic as a giant Shared Memory (Register Map). This is the "secret sauce" for its high-speed performance.

How it works: Data sent from the Host PC (LinuxCNC) travels through the W5500 and is written directly to specific addresses inside the FPGA. For instance, address 0x01 might control Motor 1's velocity, while 0x02 sets the PWM duty cycle.

Code Implementation: The Verilog code utilizes massive case statements and address decoders. When an SPI command arrives, the data is routed to the corresponding hardware module (StepGen, PWM, etc.) at the speed of hardware wires.

The Benefit: Zero CPU intervention. Commands move at the speed of electricity, not at the speed of a software instruction loop.

2. High-Resolution StepGen (DDS Technology)

The stepgen.v module, which handles motor pulses, uses a technique called Direct Digital Synthesis (DDS). This is leagues ahead of traditional software-based "bit-banging."

The DDS Principle: Instead of a simple loop that toggles a pin, RioCore uses a 32-bit Phase Accumulator.

Code Implementation: This calculation is performed in parallel for every axis on every single nanosecond-scale system clock cycle.

The Benefit: You can run multiple motors simultaneously without any "crosstalk" or speed degradation. It ensures perfectly smooth motion even at ultra-high frequencies.

3. Dedicated W5500 SPI Finite State Machine (FSM)

Since the W5500 uses a specific frame structure (Address + Control + Data), RioCore implements a custom Finite State Machine (FSM) to talk to it as efficiently as possible.

State Transitions: The logic is strictly governed by states: IDLE → SEND_ADDR → SEND_CONTROL → DATA_PHASE → DONE.

Code Implementation: The FSM is synchronized with the W5500’s hardware interrupt (INT) pin. The moment a network packet arrives, the FPGA logic reacts instantly.

The Benefit: This architecture minimizes "Network-to-Motor" latency. It ensures that the time between a PC sending a command and the motor moving is kept to an absolute minimum.

🌟 Applications

Professional CNC Machines: Retrofitting old mills or building new high-speed routers.

Robotics: Controlling multi-axis robotic arms with ROS (Robot Operating System) integration.

3D Printing: Advanced printers requiring ultra-fine micro-stepping and complex kinematics.

Data Acquisition: High-speed, real-time sensor monitoring via Ethernet.

RioCore democratizes high-end motion control by combining the parallel processing power of FPGAs with the networking simplicity of the W5500. It is a must-try for any developer looking to push the boundaries of real-time hardware.

🤖 RioCore Q&A

Q1: What is the RioCore project and what problem does it solve?

A: RioCore is an open-source FPGA-based real-time IO (RIO) system designed primarily for motion control platforms like LinuxCNC. It solves the high-cost barrier of professional motion control by allowing users to use inexpensive, generic FPGA boards (e.g., Tang Nano, iCE40, ECP5) to replace expensive proprietary hardware like Mesa boards. By moving time-critical tasks from software to hardware logic, it eliminates "jitter" and ensures nanosecond-precision control.

Q2: How does RioCore utilize the WIZnet W5500 chip?

A: In the RioCore architecture, the WIZnet W5500 serves as a hardware TCP/IP offload engine. Instead of using FPGA gates to process complex network protocols, the W5500 handles the Ethernet stack internally. It receives UDP packets from the host PC and transmits them to the FPGA via a high-speed SPI interface. This configuration ensures ultra-low latency and reliable communication, which is critical for the 1ms servo loops required in professional CNC operations.

Q3: Why does the RioCore GUI show an ESP32 module alongside the FPGA?

A: As seen in the project's Setup-GUI, the ESP32 can be used as a versatile network bridge. While the W5500 is used for wired Ethernet, the ESP32 provides an alternative for wireless (Wi-Fi) UDP communication or acts as a co-processor to handle flexible pin mapping and initialization. In this setup, the ESP32 manages the "mouth" (networking), while the FPGA (like the iCE40 or Tang Nano) manages the "muscle" (real-time high-speed IO).

Q4: What are the technical advantages of using DDS (Direct Digital Synthesis) in RioCore?

A: RioCore implements DDS technology within its Verilog stepgen.v module to generate motor pulses. Unlike software-based systems that toggle pins in a loop, DDS uses a 32-bit phase accumulator to calculate pulse timing mathematically:

This method allows for virtually continuous frequency resolution and ensures that all motor axes are synchronized to the same system clock with zero jitter.

Q5: Do I need to know Verilog or FPGA programming to use RioCore?

A: No, one of the primary features of RioCore is its Python-based code generator (rio-generator). Users define their hardware configuration—such as the number of motor axes, PWM pins, and encoder inputs—through a graphical user interface (GUI). The system then automatically synthesizes the necessary Verilog code and LinuxCNC configuration files (HAL/INI), making FPGA technology accessible to hobbyists and makers without HDL expertise.

Q6: What hardware is compatible with RioCore?

A: RioCore is designed for high portability and supports a variety of cost-effective FPGA development boards, including:

Sipeed Tang Nano 9K/20K (Gowin)

iCE40 HX8K (Lattice)

ECP5 and Xilinx Artix-7

Communication: WIZnet W5500 (Ethernet) or ESP32 (Wireless/Bridge)