STM32 Blue Pill ADC Streaming over W5100

A Blue Pill firmware prototype streams dual ADC samples through DMA buffers to a TCP server using an Arduino Ethernet stack.

Overview

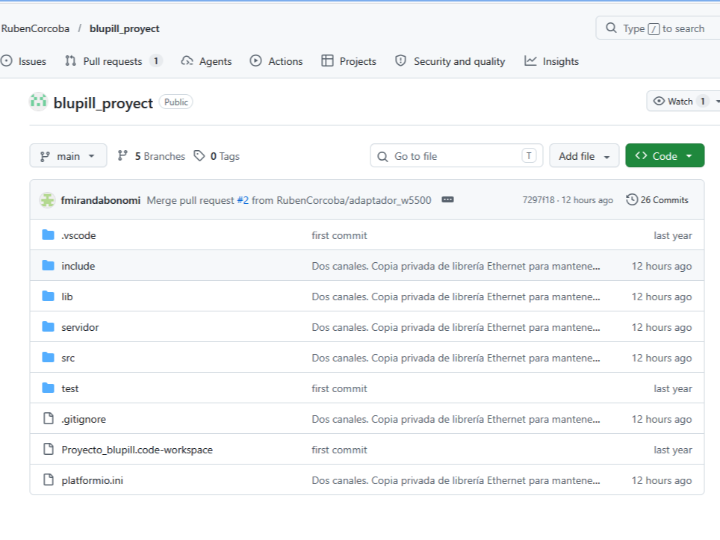

This repository is a PlatformIO-based embedded firmware project for an STM32F103C8 “Blue Pill” board using the Arduino framework. The public repository has no descriptive README, so the technical intent must be inferred from the project configuration and source code rather than from formal documentation. The repository is mainly C++ with a small C component, and it includes firmware source, a local Ethernet library, and a small PC-side server program.

The firmware configures ADC sampling on the STM32, moves samples into memory through DMA, and sends filled buffers over a TCP connection. The receiving side is represented by a Windows socket server listening on port 4000 and printing received samples as signed I/Q pairs.

Main Content

The central design is a streaming pipeline rather than a simple sensor-reading example. The firmware defines two ADC channels, two bytes per channel, and 512 samples per buffer segment, producing a repeated block of interleaved sample data. A double buffer is exposed through shared counters that separate “buffers filled by DMA” from “buffers already processed by the main loop.”

The acquisition path uses ADC plus DMA in circular mode. The DMA interrupt handler reacts to half-transfer and transfer-complete events, increments a filled-buffer counter, and uses GPIO toggling as a lightweight timing or activity indicator. This structure reduces the amount of CPU work needed for sample capture, because the CPU does not need to manually copy every ADC result from a peripheral register into RAM.

The main loop does not perform sampling directly. It checks whether a newly filled buffer is available, sends exactly one buffer when the producer and consumer counters differ by one, and resynchronizes the consumer counter if more than one buffer has accumulated. That resynchronization behavior is a practical boundary: the system prefers dropping stale backlog state over allowing the transmit side to keep falling behind silently.

The network side uses an Arduino Ethernet-compatible API with an EthernetClient. The firmware initializes a fixed MAC address, a fixed local IP address, and a fixed server IP address, then connects to TCP port 4000 before writing sample buffers. The repository includes an Ethernet library whose metadata describes local and Internet network connectivity through the Arduino Ethernet stack.

The Ethernet controller path is tied to the WIZnet W5100 family interface. The firmware comment identifies W5100 initialization, and the included Ethernet library has W5100, W5200, and W5500 hardware detection paths. The WIZnet W5100 is an embedded Ethernet controller integrating TCP/IP stack, Ethernet MAC, and PHY, which makes it a suitable offload component for a small MCU that should focus on deterministic sampling and buffer handoff rather than full Ethernet protocol handling.

The host-side server is intentionally minimal. It uses Winsock, listens on TCP port 4000, receives byte blocks, interprets them as pairs of signed 16-bit values, and prints them as complex-style I/Q samples. This indicates that the Blue Pill node is not intended to be a full analysis instrument by itself; it acts as an acquisition and transport front end, while interpretation or visualization is expected to happen on a host system.

System Context

The project fits a small embedded data-acquisition role. The STM32F103C8 board captures analog inputs, DMA decouples acquisition from CPU timing, the WIZnet Ethernet controller provides wired network transport, and the PC server receives and interprets the raw sample stream. This is closer to a measurement transport prototype than to a complete oscilloscope, SDR receiver, or production data logger.

Compared with a simpler polling or serial-output approach, this structure separates acquisition timing from transport timing. Sampling is driven by ADC and DMA events, while Ethernet transmission happens only after a buffer boundary is reached. That separation is the main technical difference: it gives the firmware a clearer boundary between real-time capture and slower network I/O.

The highest-cost failure point is the boundary between DMA buffer production and TCP buffer transmission. If ADC sampling fills buffers faster than Ethernet can send them, the system must either drop data, resynchronize, or block. The current source chooses explicit resynchronization when the consumer falls behind, which is safer than pretending every sample was delivered, but it also means the stream may lose continuity under load.

Architecture / Design Considerations

The architecture can be read as four cooperating layers.

First, the ADC layer converts analog inputs into digital samples. The public code shows two logical ADC channels represented as 16-bit values per sample.

Second, the DMA layer transfers ADC data into RAM using a circular double-buffer pattern. The half-transfer and transfer-complete interrupts divide the buffer into chunks that the main loop can send without stopping acquisition.

Third, the Ethernet layer sends completed chunks to a fixed TCP server. The WIZnet W5100 role is important here because its hardwired TCP/IP, MAC, and PHY reduce the MCU-side networking burden. The included library still has to drive the chip over SPI, and the repository contains customized low-level W5100 transfer code using SPI2 DMA paths, so the Ethernet side is not merely a plug-in abstraction.

Fourth, the host server acts as a decoding endpoint. It assumes that received bytes align to a structure containing two signed 16-bit fields, named as I and Q. That assumption is useful for simple inspection, but it also defines a fragile interface: if byte order, alignment, channel order, or packet framing changes, the host output can become misleading without necessarily failing loudly.

Removing any one of these components changes the character of the system. Without DMA, the firmware becomes more CPU-bound and less suited to continuous sample capture. Without the WIZnet Ethernet path, the project becomes only a local ADC acquisition example unless another transport is added. Without the host server, the firmware still captures and sends buffers, but the system no longer demonstrates end-to-end sample recovery.

Possible Implications

This project is useful as a compact reference for a low-cost Ethernet-connected acquisition node. Its value is not in polish or documentation, because the repository currently provides little public explanation. Its value is in the way it combines ADC, DMA buffering, and WIZnet-based TCP transport into a small firmware pipeline.

The design also exposes the main engineering tradeoff. The system can collect and forward sample blocks, but the repository does not document sampling rate validation, packet-loss handling, timestamping, framing metadata, calibration, or recovery behavior after network interruption. Those omissions matter if the design is reused for measurement work where continuity, timing, or traceability are important.

Conclusion

This repository should be understood as an embedded streaming prototype for STM32 Blue Pill and WIZnet Ethernet, not as a finished measurement product. Its design shows a reasonable separation between ADC capture, DMA buffering, and TCP transmission, while leaving several production-level questions unresolved. The most important judgment point is whether the network path can keep up with the ADC buffer rate; if it cannot, the system’s own resynchronization behavior makes data loss possible rather than hidden.

전체 개요

이 저장소는 STM32F103C8 기반 Blue Pill 보드에서 ADC 데이터를 연속적으로 수집하고, DMA 더블 버퍼를 거쳐 Ethernet TCP 서버로 전송하는 임베디드 수집 노드 성격의 프로젝트입니다. 저장소 자체에는 설명용 README가 거의 없고, GitHub 페이지도 별도 설명이 없다고 표시되어 있습니다. 그래서 이 큐레이션은 공개 코드와 설정 파일을 기준으로 보수적으로 해석한 것입니다.

핵심 흐름은 다음과 같습니다.

ADC 입력 → DMA 순환 버퍼 → 버퍼 완료 인터럽트 → main loop 전송 판단 → W5100 계열 Ethernet TCP 전송 → PC 서버 수신

여기서 이 프로젝트의 본질은 “Blue Pill로 Ethernet을 붙였다”가 아니라, 작은 MCU에서 샘플링과 통신의 시간축을 분리하려는 구조에 있습니다. 폴링으로 ADC를 읽고 바로 출력하는 예제와 달리, DMA가 샘플 수집을 맡고 CPU는 채워진 버퍼를 네트워크로 밀어내는 역할을 합니다. 임베디드에서 늘 그렇듯, 문제는 코드를 쓰는 것이 아니라 “어디서 밀리면 망하는지”를 아는 것입니다.

문제의식과 기술적 맥락 재구성

일반적인 초급 ADC 예제는 CPU가 ADC 값을 읽고, 그 값을 Serial이나 화면 출력으로 확인하는 구조가 많습니다. 이런 구조는 이해하기 쉽지만, 샘플 수가 많아지거나 일정한 수집 간격이 중요해지면 CPU가 매번 ADC 결과를 직접 처리해야 해서 병목이 생깁니다. STM32 계열에서 ADC와 DMA를 함께 쓰는 이유는, ADC 결과를 CPU가 매번 건드리지 않고 메모리로 이동시키기 위해서입니다. 이 부분은 STM32 ADC/DMA 일반 설명에서도 “DMA가 peripheral에서 memory로 데이터를 옮겨 CPU 부담을 줄인다”는 방식으로 설명됩니다.

이 저장소의 코드는 그 문제를 DMA 순환 버퍼와 half-transfer / transfer-complete 인터럽트로 풀고 있습니다. DMA1_Channel1_IRQHandler()에서 절반 버퍼가 찼을 때와 전체 버퍼가 찼을 때 각각 카운터를 증가시키고, main loop는 이 카운터를 보고 새 버퍼가 생겼는지 판단합니다.

추론임: 이 구조는 단발성 센서 읽기보다 연속 샘플 스트림을 외부 PC로 넘기는 실험용 수집기에 가깝습니다. 특히 서버 코드가 받은 데이터를 int16_t i, q 쌍으로 해석해 i+qj 형태로 출력하는 점을 보면, 단순 전압 로깅보다는 I/Q 형태의 샘플 확인 또는 신호 처리 실험을 염두에 둔 흔적이 있습니다. 다만 저장소에 신호 처리 목적이나 샘플링 주파수 설명이 없으므로, “I/Q 신호 수집 장비”라고 단정할 수는 없습니다.

기술 흐름 설명

1. 보드와 빌드 환경

platformio.ini는 genericSTM32F103C8, bluepill_f103c8, Arduino framework를 사용하도록 설정되어 있습니다. 즉, STM32Cube HAL 중심 프로젝트가 아니라 PlatformIO + Arduino 추상화 위에서 일부 레지스터 직접 접근을 섞은 형태입니다.

이 선택은 장단점이 분명합니다. Arduino Ethernet API를 활용하면 TCP 전송 코드는 단순해지지만, ADC/DMA처럼 타이밍과 레지스터 제어가 중요한 부분은 결국 저수준 접근이 필요합니다. 이 프로젝트가 바로 그 혼합형입니다. 인간이 추상화를 만들고 다시 그 밑을 파헤치는 장면, 참 일관된 혼돈입니다.

2. ADC 데이터 구조

헤더 파일에는 2개 ADC 채널, 채널당 2바이트, 샘플당 4바이트라는 구조가 정의되어 있습니다. 버퍼 단위는 NMUESTRAS_BUFFER = 512로 잡혀 있고, 실제 버퍼는 2개 영역을 갖는 형태입니다.

즉 한 샘플은 대략 다음처럼 해석됩니다.

sample = channel_0 16-bit + channel_1 16-bit

buffer = 512 samples × 4 bytes

double buffer = buffer[0], buffer[1]주의할 점은 서버 쪽에서는 이 데이터를 int16_t i, q 구조체로 해석한다는 것입니다. MCU 쪽 채널 순서와 서버 쪽 I/Q 의미가 정확히 어떻게 대응되는지는 코드상 완전히 문서화되어 있지 않습니다. 따라서 실제 측정 장비로 확장하려면 “채널 0이 I인가, Q인가”, “엔디언은 고정인가”, “샘플 경계가 TCP 수신 경계와 항상 맞는가”를 별도로 검증해야 합니다.

3. DMA 기반 수집

ADC_DMA_Init()은 ADC와 DMA를 설정하고, DMA1 Channel 1의 half-transfer interrupt와 transfer-complete interrupt를 켭니다. 인터럽트가 발생하면 cuenta_buffers_cargados가 증가하고, main loop는 이 값을 기준으로 전송할 버퍼가 있는지 봅니다.

이 방식의 핵심은 샘플 수집과 전송을 직접 결합하지 않는 것입니다. ADC는 계속 샘플을 만들고, DMA는 메모리에 채우고, CPU는 버퍼 단위로 뒤따라갑니다. 기존의 단순 접근과 비교했을 때 가장 큰 차이는 CPU가 “샘플 하나하나”가 아니라 “완료된 블록”을 처리한다는 점입니다.

4. main loop의 전송 판단

loop()는 새 버퍼가 없으면 바로 return합니다. 새 버퍼가 정확히 하나 있으면 해당 버퍼를 transmite()로 보내고, 처리 카운터를 증가시킵니다. 그런데 생산된 버퍼가 처리된 버퍼보다 둘 이상 앞서 있으면, 따라잡으려고 모든 버퍼를 보내지 않고 cuenta_buffers_vistos = cuenta_buffers_cargados로 동기화합니다.

이 부분이 이 시스템에서 가장 중요한 판단 지점입니다. 전송이 늦어져 버퍼가 밀리면, 이 코드는 연속성을 보장하려 하지 않고 현재 위치로 건너뜁니다. 즉 “데이터 손실을 숨기면서 밀린 데이터를 다 보내는 척”하는 구조가 아니라, 뒤처졌을 때 최신 상태로 맞추는 구조입니다. 실험용 실시간 스트림이라면 납득 가능한 선택이지만, 모든 샘플을 보존해야 하는 로거라면 위험한 선택입니다.

왜 이런 구조가 나왔는지에 대한 해설

추론임: 이 구조는 STM32F103C8의 제한된 CPU, RAM, 네트워크 처리 여유를 고려한 타협으로 보입니다. Blue Pill은 저렴하고 접근성이 좋지만, 고속 샘플링과 네트워크 송신을 동시에 안정적으로 처리하려면 CPU가 모든 일을 직접 하기 어렵습니다. 그래서 ADC 수집은 DMA에 맡기고, Ethernet은 WIZnet W5100 계열 칩과 Arduino Ethernet API에 위임하는 구조가 자연스럽습니다.

WIZnet W5100은 TCP/IP stack, Ethernet MAC, PHY를 한 칩에 통합한 embedded Ethernet controller로 설명됩니다. 이 말은 MCU가 TCP/IP 전체를 소프트웨어로 직접 구현하지 않아도 된다는 뜻입니다. 이 프로젝트에서 W5100 계열 Ethernet controller는 “통신 보조 장치”에 가깝고, 시스템의 중심 역할은 ADC 수집과 버퍼 흐름 제어에 있습니다.

왜 보조 수단인가 하면, 이 시스템의 목적은 Ethernet 컨트롤러 자체를 보여주는 것이 아니라 수집된 샘플을 외부로 내보내는 것이기 때문입니다. W5100이 빠지면 수집 노드는 네트워크 출력 경로를 잃지만, ADC/DMA 수집 구조 자체는 남습니다. 반대로 ADC/DMA가 빠지면 이 프로젝트는 단순 TCP 예제에 가까워져서 시스템 성격이 크게 바뀝니다.

설계 선택의 배경

DMA 더블 버퍼

더블 버퍼는 생산자와 소비자를 분리하기 위한 전형적인 구조입니다. 여기서는 DMA가 생산자이고, Ethernet 송신 루틴이 소비자입니다. 한쪽 버퍼가 채워지는 동안 다른 쪽 버퍼를 전송할 수 있으므로, 샘플링과 전송이 서로를 덜 방해합니다.

다만 더블 버퍼는 만능이 아닙니다. 네트워크 전송이 지속적으로 느리면 버퍼 2개만으로는 버티지 못합니다. 이 저장소의 main loop가 backlog 발생 시 동기화해 버리는 이유도 그 한계를 코드 차원에서 인정한 것으로 볼 수 있습니다.

고정 IP 기반 TCP 전송

코드에는 장치 IP와 서버 IP가 고정값으로 들어가 있습니다. 장치는 192.168.1.33, 서버는 192.168.1.120, 포트는 4000으로 보입니다. DHCP나 자동 탐색보다 실험 환경에서 빠르게 확인하기 쉬운 선택입니다.

추론임: 이 선택은 제품형 네트워크 장비보다는 실험실 또는 로컬 네트워크에서 직접 연결해 데이터를 확인하는 개발 단계에 어울립니다. 운영 환경이 바뀌면 IP 설정, 재접속, 서버 부재 처리, timeout 정책이 추가되어야 합니다.

W5100 계열 Ethernet 사용

저장소에는 Arduino Ethernet library가 포함되어 있고, 라이브러리 설명은 Arduino Ethernet 보드나 실드를 통해 네트워크 연결을 가능하게 한다고 되어 있습니다. 내부 w5100.cpp에는 W5100, W5200, W5500 감지 로직이 있으며, W5100 경로와 SPI/DMA 전송 코드도 보입니다.

추론임: 실제 하드웨어가 W5100인지, W5500인지, 또는 W5100 호환 모듈인지는 저장소 문서만으로 완전히 확정하기 어렵습니다. 하지만 소스 주석에 W5100 초기화가 명시되어 있고, 파일명과 라이브러리 경로가 W5100 중심이므로, 큐레이션상 “W5100 계열 Ethernet controller 기반”으로 보는 것이 가장 보수적인 해석입니다.

제약 조건

이 프로젝트를 그대로 재사용할 때 가장 먼저 봐야 할 제약은 세 가지입니다.

첫째, 데이터 연속성 보장 여부입니다. 버퍼가 밀리면 코드가 카운터를 동기화하므로, 모든 샘플을 보존하는 구조가 아닐 수 있습니다. 이건 로깅 장비에서는 큰 문제입니다.

둘째, TCP는 메시지 경계를 보장하지 않습니다. 서버 코드는 수신된 recvbuf를 곧바로 Sample_s 배열로 캐스팅합니다. TCP 수신 단위가 샘플 구조체 경계와 맞지 않으면 일부 샘플 해석이 깨질 수 있습니다. 현재 코드에는 프레임 헤더, sequence number, payload length, checksum 같은 안정화 장치가 보이지 않습니다.

셋째, 하드웨어 핀과 주석의 불일치 가능성입니다. main.cpp 상단 주석에는 SPI1 remap 핀 이야기가 나오지만, bsp_init()에서는 PB15, PB14, PB13, PB12 조합을 사용합니다. 정보 제한: 실제 회로도나 배선도가 없으므로 어느 쪽이 최종 하드웨어 기준인지 단정할 수 없습니다.

대안 가능성

이 구조를 확장한다면 몇 가지 방향이 있습니다.

USB CDC로 보내는 방식은 구현이 단순하고 Blue Pill에서 접근성이 좋습니다. 하지만 장거리 배선, 네트워크 연결성, host 분리 측면에서는 Ethernet보다 불리합니다.

UDP 전송은 TCP보다 지연이 예측 가능하고 스트리밍에 가벼울 수 있습니다. 대신 손실, 순서, 재전송을 애플리케이션에서 직접 다뤄야 합니다. 샘플 누락을 허용할 수 있고 지연이 더 중요하다면 UDP도 검토할 만합니다.

W5500 같은 더 널리 쓰이는 WIZnet Ethernet controller로 옮기는 것도 가능합니다. 실제로 포함된 Ethernet library는 W5100, W5200, W5500 감지 경로를 갖고 있습니다. 다만 하드웨어 배선, SPI 속도, 버퍼 크기, 라이브러리 최적화 경로가 달라질 수 있으므로 단순 치환으로 끝난다고 보면 곤란합니다.

생소한 개념에 대한 풀어쓴 설명

DMA는 CPU 대신 주변장치와 메모리 사이의 데이터 이동을 처리하는 장치입니다. ADC 샘플이 계속 생길 때 CPU가 매번 값을 읽으면 CPU 시간이 샘플 복사에 낭비됩니다. DMA를 쓰면 ADC 결과가 자동으로 RAM 버퍼에 쌓이고, CPU는 버퍼가 찼다는 이벤트만 처리하면 됩니다.

Half-transfer interrupt는 버퍼의 절반이 찼을 때 발생하는 신호입니다. Transfer-complete interrupt는 버퍼 전체가 찼을 때 발생합니다. 이 둘을 이용하면 하나의 큰 순환 버퍼를 두 조각처럼 다룰 수 있고, 한쪽이 채워지는 동안 다른 쪽을 처리할 수 있습니다.

WIZnet W5100 계열 칩은 MCU가 Ethernet PHY와 TCP/IP 처리를 모두 직접 부담하지 않도록 도와주는 Ethernet controller입니다. MCU 입장에서는 SPI 등을 통해 소켓 API에 가까운 방식으로 데이터를 주고받을 수 있습니다. 다만 “모든 네트워크 문제가 사라진다”는 뜻은 아닙니다. 연결 실패, 송신 지연, 버퍼 부족, 재접속 정책은 여전히 시스템 설계자가 다뤄야 합니다.

시스템 구성 및 선택지 해석

이 시스템을 역할별로 나누면 다음과 같습니다.

| 구성요소 | 역할 | 제거 시 변화 |

|---|---|---|

| STM32F103C8 Blue Pill | ADC 제어, DMA 설정, 버퍼 관리 | 전체 수집 노드가 사라짐 |

| ADC + DMA | 연속 샘플 수집과 RAM 저장 | 단순 CPU polling 구조로 후퇴 |

| Double buffer | 수집과 전송 사이 완충 | 전송 지연이 곧바로 샘플 손실이나 blocking으로 이어질 가능성 증가 |

| WIZnet W5100 계열 Ethernet | TCP 기반 유선 전송 경로 | USB/Serial 등 다른 출력 수단 필요 |

| PC Winsock server | TCP 수신 및 I/Q 샘플 표시 | end-to-end 검증 경로 상실 |

특정 구성요소를 제거했을 때 가장 크게 성격이 바뀌는 것은 ADC/DMA입니다. Ethernet을 바꾸면 “전송 수단”이 바뀌지만, ADC/DMA를 제거하면 이 프로젝트는 연속 수집 노드가 아니라 일반 MCU 통신 예제로 성격이 바뀝니다.

반대로 W5100 계열 Ethernet을 제거하면 실시간 수집 구조는 남지만, 시스템 경계가 보드 내부로 닫힙니다. 즉 “데이터를 만든다”와 “데이터를 쓸 수 있게 외부로 보낸다” 사이의 차이가 생깁니다. 임베디드에서 이 차이를 무시하면 나중에 꼭 누군가 oscilloscope 앞에서 침묵하게 됩니다.

내부 관점에서의 시사점

이 저장소는 문서화가 부족하지만, 기술 구조 자체는 발표용으로 다룰 가치가 있습니다. 특히 작은 MCU에서 ADC 샘플링과 TCP 전송을 동시에 다룰 때 어떤 경계가 생기는지 잘 보여줍니다.

가장 중요한 시사점은 버퍼 경계가 시스템 신뢰성의 경계라는 점입니다. ADC/DMA는 데이터를 만들고, Ethernet은 데이터를 내보내지만, 둘 사이 속도가 맞지 않으면 손실 또는 지연이 발생합니다. 이 프로젝트는 backlog가 생겼을 때 동기화하는 코드를 갖고 있으므로, “모든 데이터를 보존하는 장비”보다는 “현재 흐름을 따라가는 스트리밍 노드”에 가깝습니다.

실제 제품 또는 안정적인 계측 장비로 발전시키려면 다음 검증이 필요합니다.

- ADC 샘플링 주기와 Ethernet 송신 처리량의 상관관계

- TCP 수신 경계가 깨졌을 때의 프레이밍 복구

- 샘플 sequence number 또는 timestamp 추가

- 네트워크 끊김 후 재접속 정책

- 실제 W5100/W5500 모듈 종류와 SPI 핀맵 확정

- host server의 endian/alignment 안전성 검증

이 저장소의 장점은 구조가 작고 직접적이라는 점입니다. 단점은 바로 그 직접성 때문에, 실패했을 때 왜 실패했는지를 알려주는 메타데이터가 거의 없다는 점입니다.

FAQ

1. 기존 polling 방식 ADC 예제와 가장 큰 차이는 무엇인가요?

가장 큰 차이는 CPU가 샘플 하나하나를 읽는 구조가 아니라, DMA가 버퍼를 채우고 CPU는 완료된 버퍼 단위로 처리한다는 점입니다. 이 덕분에 샘플 수집과 Ethernet 송신 사이에 완충 계층이 생깁니다.

2. 왜 WIZnet W5100 계열 Ethernet controller가 보조 수단으로 해석되나요?

이 프로젝트의 중심 목적은 Ethernet controller 자체의 기능 검증이 아니라 ADC 샘플을 외부로 전송하는 것입니다. W5100 계열 칩은 TCP/IP, MAC, PHY 부담을 줄여주는 통신 보조 계층이고, 시스템의 본질은 ADC/DMA 기반 수집 흐름에 있습니다.

3. 실패 비용이 가장 큰 구간은 어디인가요?

DMA 버퍼 생산 속도와 TCP 전송 속도가 맞지 않는 구간입니다. 전송이 늦어지면 버퍼가 밀리고, 현재 코드는 backlog가 생겼을 때 처리 카운터를 최신 생산 카운터에 맞추는 방식이라 샘플 연속성이 깨질 수 있습니다.

4. TCP로 받으면 샘플 경계가 자동으로 보장되나요?

아닙니다. TCP는 byte stream이므로 recv() 한 번이 MCU에서 write()한 한 버퍼와 정확히 대응된다고 보장하지 않습니다. 서버 코드가 받은 바이트를 바로 int16_t i, q 구조로 해석하기 때문에, 실사용 확장 시 프레임 헤더나 길이 정보가 필요할 수 있습니다.

5. 특정 구성요소를 제거하면 시스템 성격이 어떻게 바뀌나요?

DMA를 제거하면 연속 수집 노드가 아니라 CPU 중심 ADC 읽기 예제에 가까워집니다. W5100 계열 Ethernet을 제거하면 외부 PC로 바로 흐르는 유선 TCP 전송 경로가 사라지고, USB나 Serial 같은 대체 전송 경로를 설계해야 합니다.

6. 이 프로젝트를 그대로 계측 장비로 봐도 되나요?

그렇게 단정하기는 어렵습니다. 공개 코드상으로는 ADC 수집과 TCP 전송의 end-to-end 흐름은 보이지만, 샘플링 주기 검증, timestamp, 손실 검출, 캘리브레이션, 재접속 처리 같은 계측 장비 수준의 장치는 확인되지 않습니다.

저자 정보

공개된 GitHub 정보 기준으로, 저장소 소유자는 RubenCorcoba 계정입니다. 해당 GitHub 프로필은 12개의 공개 저장소를 가진 계정으로 표시되며, 이 저장소는 C++ 중심 프로젝트로 표시됩니다.

정보 제한: 이 저장소와 직접 연결된 소속 기관, 연구실, 회사, 공식 프로젝트 배경은 저장소 페이지에서 확인되지 않습니다. 추론임: 공개 저장소 목록에 STM32 Blue Pill, PlatformIO, C/C++ 기반 프로젝트가 보이므로 임베디드 실험 또는 교육/개인 개발 맥락일 가능성은 있지만, 이를 저자의 공식 전문 분야나 소속의 근거로 삼을 수는 없습니다.