Nanosecond-Skew 24-bit TMR (Tunnel Magnetoresistance) Array DAQ for Geomagnetic Anomalies, W5500

Low-noise TMR sensor array with 24-bit synchronized ADCs, adaptive power modes, and W5500 Ethernet streaming for geomagnetic anomaly monitoring.

Overview

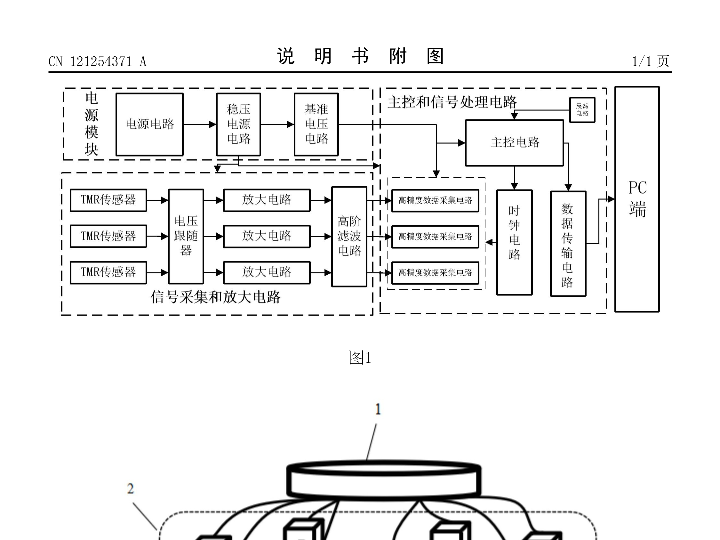

This patent describes a geomagnetic anomaly detection device built around a multi-sensor TMR (Tunnel Magneto-Resistance) array and a carefully engineered low-noise signal chain. The design goal is long-duration, high-precision field operation where external interference, sensor noise floor, and power constraints often degrade measurement quality.

Key elements include: triaxial TMR sensing units (orthogonally arranged), front-end impedance decoupling via voltage followers, low-noise instrumentation amplification with single-resistor gain setting, passive analog filtering, and multi-channel high-resolution ADC sampling synchronized by a low-jitter clock. Processed data is transmitted to a host computer through Ethernet, explicitly using a WIZnet W5500 hardware TCP/IP offload controller.

Main Content

What problem is being solved

Geomagnetic anomaly detection requires resolving extremely small magnetic field changes under real-world conditions (power limits, EMI, cable runs, and long unattended operation). The patent frames common shortcomings of existing systems as:

- Noise and interference reducing usable resolution (sensor noise floor + circuit noise + environmental coupling)

- Complex architectures that increase power consumption and reduce robustness

- Multi-channel array systems suffering from sampling mismatch, distortion, and degraded precision without tight synchronization

Core idea: treat the whole chain as a precision DAQ system

Instead of focusing only on sensor sensitivity, the invention designs an end-to-end data acquisition (DAQ) chain where each stage protects signal integrity:

- TMR triaxial array to detect weak geomagnetic variations

- Front-end buffering (isolation) to prevent impedance coupling that can increase noise or distort gain

- Instrumentation amplifier optimized for low noise and gain consistency

- Analog filtering to suppress power-line and broadband interference before digitization

- Synchronized 24-bit ADC sampling for time-aligned multi-channel array measurements

- Embedded processing + adaptive power strategy to reduce energy use during stable periods and increase capture/throughput during anomalies

- Ethernet data link using WIZnet W5500 to send processed data to the host reliably over wired networks

DAQ specifics highlighted in the disclosure

- Tri-axial sensing unit: built by orthogonally arranging three single-axis TMR chips; shielding is used in non-measurement directions to reduce disturbance.

- Isolation circuit: a voltage follower per channel to decouple sensor internal resistance from the downstream network.

- Low-noise amplification: a low-power instrumentation amplifier (example given: INA333), using a single resistor to set gain and avoid mismatch errors from dual-resistor structures.

- ADC subsystem: multiple 24-bit ADC channels implemented via parallel multi-channel converters (example: three ADS131M08 chips providing 24 channels). A low-jitter clock distributor (example: AD9523-1) provides a unified sampling clock so channel sampling skew is constrained (claimed ≤ 1 ns).

- MCU processing: example MCU is STM32F407VET6, handling acquisition, buffering, timestamps, event detection, and link management.

- Ethernet transport: WIZnet W5500 is used as the hardware TCP/UDP/IP stack device connected via SPI (example mentions up to 80 MHz), with internal TX/RX buffers and stable throughput for field deployment. The reason to use W5500-class hardware offload is to reduce MCU workload/latency jitter and improve link robustness compared to software stacks under tight power and real-time constraints.

- Power and reference: low-noise LDOs and a shared precision reference framework are used to stabilize analog performance. The PCB uses analog/digital partitioning with single-point bridging (e.g., ferrite bead) to limit digital noise injection into the analog front end.

System Context

The device targets long-term geomagnetic anomaly monitoring for applications such as geophysical exploration, defense/security monitoring, and complex environments where noise, EMI, and power constraints are expected. The host computer provides data logging, real-time visualization, alarming, and calibration management.

Architecture / Design Considerations

Why the architecture is an array + synchronized sampling

An array enables spatial discrimination and improves anomaly detection capability, but only if channels are time-aligned and consistently conditioned. The design invests in clock distribution and multi-channel synchronization because array processing becomes unreliable when channel skew and phase mismatch are comparable to the dynamics being observed.

Largest “failure cost” point in the system

The highest-cost failure is corrupting low-level magnetic signals before digitization (impedance coupling, EMI pickup, ground noise, reference instability). Once the analog signal is polluted, no amount of digital post-processing can reliably restore the true anomaly signal.

Why Ethernet and why WIZnet W5500 specifically

For field instrumentation, wired Ethernet provides stable long-range transport without the unpredictability of wireless links. The WIZnet W5500 integrates the TCP/IP stack in hardware, reducing firmware complexity and MCU cycles, which helps preserve real-time acquisition behavior and supports deterministic data streaming under constrained power and compute budgets.

What changes if a key component is removed

- Remove the isolation buffers: sensor-loading and impedance coupling can increase noise and distort gain calibration.

- Remove unified low-jitter clocking: channel-to-channel skew grows, degrading array coherence and increasing false anomalies.

- Replace W5500 hardware offload with a software stack: MCU load and timing jitter can increase, potentially forcing reduced sampling/processing or causing transport instability during anomaly bursts.

Possible Implications

The disclosed approach generalizes to other low-level sensor-array DAQ problems where the limiting factor is not sensor sensitivity alone, but the full measurement chain: buffering, noise discipline, synchronization, and reliable streaming. The adaptive power/throughput strategy also fits battery-backed monitoring deployments.

Conclusion

CN121254371A presents a precision DAQ-centered geomagnetic anomaly detector: a TMR triaxial array with impedance isolation, low-noise amplification and filtering, tightly synchronized multi-channel 24-bit digitization, embedded event-aware processing, and an Ethernet uplink implemented with the WIZnet W5500 hardware TCP/IP controller to stream reliable data in long-duration field scenarios.

전체 개요

본 특허(CN121254371A)는 TMR(터널 자기저항) 3축 센서 어레이를 기반으로, 저잡음·고정밀·저전력 조건에서 **지자기(geomagnetic) 이상(anomaly)**을 장시간 안정적으로 측정하기 위한 정밀 DAQ(데이터 수집) 시스템을 제안합니다.

핵심은 “센서를 좋은 걸 쓰면 끝”이 아니라, 센서–아날로그 전단–증폭–필터–ADC–동기 클럭–MCU 처리–유선 이더넷 전송까지 전체 사슬에서 잡음과 왜곡의 원인을 체계적으로 줄이는 설계입니다.

특히 데이터 전송부에 WIZnet W5500(하드웨어 TCP/IP 오프로딩)을 명시하여, 임베디드 MCU가 소프트웨어 네트워크 스택에 잡아먹히지 않도록 하고 DAQ의 시간 결정성/안정성을 확보하려는 구성이 눈에 띕니다.

문제의식과 기술적 맥락 재구성

지자기 이상 탐지는 “큰 신호를 보기”가 아니라 아주 작은 변화를 오래 안정적으로 보기에 가깝습니다. 이때 품질을 망가뜨리는 주범은 대체로 아래 3가지입니다.

- 센서 자체의 노이즈 플로어 + 바이어스 조건

- TMR의 장점은 매우 약한 자기장 변화를 잘 잡는 것이지만, 바이어스 전류/구동 조건에 따라 노이즈가 커질 수 있습니다.

- 아날로그 전단(전압/임피던스/접지/레퍼런스)에서의 오염

- “화이트 노이즈(열잡음/샷노이즈)” 같은 근본 잡음뿐 아니라, 케이블/접지/디지털 스위칭 노이즈가 아날로그 신호를 망가뜨립니다.

- 다채널 어레이에서의 동기화 실패(시간축 불일치)

- 어레이는 공간 정보를 얻는 대신, 채널 간 타이밍이 어긋나면 “가짜 이상”이 만들어집니다.

이 특허는 위 세 문제를 DAQ 체인 관점에서 각각에 대응합니다.

기술 흐름 설명: 신호 / 데이터 / 동작 순서 중심

아래는 특허가 제시한 신호 흐름을 DAQ 파이프라인으로 정리한 것입니다.

- 3축 TMR 센서 어레이에서 아날로그 신호 생성

- 단일 축 TMR 칩 3개를 직교 배치해 3축을 구성합니다.

- 측정하지 않는 방향에는 차폐(shielding) 구조를 둬 외란을 줄입니다.

- Isolation(버퍼)로 센서 임피던스-후단 회로 결합 차단

- 전압 팔로워(예: OPA333)로 입력 임피던스를 매우 크게 만들어, 센서가 후단 회로에 의해 “로드”되는 현상을 줄입니다.

- 이 단계는 “신호를 키우기”보다 신호를 망가뜨리지 않기에 가깝습니다.

- 저잡음 계측 증폭(Instrumentation Amp) + 단일 저항 이득 설정

- INA333 같은 저잡음 계측 증폭기를 사용하고, 이득을 단일 저항으로 설정하여 채널 간 오차(저항 매칭 문제)를 줄입니다.

- 어레이는 채널 수가 늘수록 “아주 작은 차이”가 누적되므로, 이득 설정 구조 자체가 품질에 직결됩니다.

- 아날로그 패시브 필터로 전원주파수(50Hz) 및 광대역 간섭 억제

- ADC로 들어가기 전에 불필요한 대역 에너지를 줄여, 샘플링 이후의 디지털 처리가 감당할 ‘오염량’을 낮춥니다.

- 24-bit ADC 다채널 동기 샘플링(병렬 ADC + 공통 클럭)

- 예시 구현으로 ADS131M08(8ch, 24bit) 3개를 사용해 총 24채널을 구성합니다.

- AD9523-1 같은 저지터 클럭 분배로 공통 샘플링 기준을 제공하여, 채널 간 샘플링 편차를 매우 작게(특허 주장: ≤1ns) 가져가려 합니다.

- 여기서 핵심은 “해상도(24-bit)” 자체보다 동기화 + 노이즈 예산 관리입니다.

- MCU(예: STM32F407)에서 전처리 + 이벤트 기반 전력/전송 전략

- 평상시(환경 안정)에는 일부 센서/전송률을 낮춰 전력 소모를 줄이고,

- 이상 감지 시에는 전체 어레이 + 전송률을 올려 ‘이벤트 윈도우’를 확보합니다.

- 즉, DAQ를 “항상 풀스펙”으로 돌리지 않고 상황에 따른 모드 전환을 넣습니다.

- 유선 Ethernet 전송: WIZnet W5500 하드웨어 TCP/IP 오프로딩

- 이 특허의 포인트 중 하나는 전송부에 WIZnet W5500을 명시한 점입니다.

- W5500은 TCP/UDP/IP 스택을 칩 내부에서 처리(하드웨어 오프로딩)하므로, MCU는 DAQ/처리 타이밍을 유지한 채 데이터를 안정적으로 내보내는 데 유리합니다.

- “그냥 이더넷”이 아니라, DAQ의 결정성과 MCU 부하 관리를 위해 하드웨어 스택을 고른 구조로 해석됩니다.

기본 개념 설명: 용어를 짚고 넘어가기

- DAQ(Data Acquisition): 센서 아날로그 신호를 신뢰 가능한 디지털 데이터로 바꾸기 위한 전체 체인(전단, 증폭, 필터, ADC, 동기화, 처리)을 의미합니다.

- TMR(Tunnel Magneto-Resistance): 자기장 변화에 따른 저항 변화를 이용하는 센서 계열 중 민감도가 높은 편으로, 약한 자기장 변화 탐지에 유리하다고 알려져 있습니다.

- Instrumentation Amplifier(계측 증폭기): 미세한 차동 신호를 공통모드 노이즈(예: 외란, 그라운드 노이즈)와 분리해 증폭하는 데 유리한 증폭기 구조입니다.

- Delta-Sigma ADC + OSR(Over-Sampling Ratio): 오버샘플링과 노이즈 셰이핑을 통해 유효 분해능/대역 내 노이즈를 개선할 수 있는 ADC 계열입니다.

- Low-jitter clock: 다채널 샘플링의 시간축 정렬을 좌우합니다. 지터/스큐가 커지면 어레이에서 위상/채널 정합이 무너집니다.

- Unified reference(공유 기준전압): 센서 구동/ADC 기준이 들쭉날쭉하면 채널 간 비교가 흔들립니다. 공통 레퍼런스를 쓰는 이유가 여기 있습니다.

왜 이런 구조가 나왔는지: 설계 선택의 배경, 제약, 대안 가능성

- 버퍼(Voltage follower)를 굳이 넣는 이유

- 센서 내부저항과 후단 회로가 결합하면, “측정하고 싶은 값”이 아니라 “회로 상호작용 결과”를 측정하는 상황이 발생할 수 있습니다.

- 특히 저레벨 신호에서는 이런 상호작용이 곧 노이즈/오프셋/비선형으로 나타납니다.

- 단일저항 이득 설정(INA333 계열)의 의미

- 어레이는 채널 수가 늘어날수록 “저항 매칭 오차”가 누적됩니다.

- 단일저항 설정은 구조적으로 오차원을 줄이는 선택입니다.

- 동기 클럭에 돈을 쓰는 이유(공통 클럭 분배)

- 어레이 분석에서 가장 위험한 건 “자기장 이상”이 아니라 “타이밍 어긋남”이 이상처럼 보이는 경우입니다.

- 즉, 동기화는 정밀도 확보를 위한 필수 비용으로 보입니다.

- WIZnet W5500을 쓰는 이유: DAQ 타이밍을 지키기 위한 네트워크 설계

- 소프트웨어 TCP/IP 스택은 MCU 시간을 많이 잡아먹고, 최악의 경우 DAQ 처리 주기 자체를 흔들 수 있습니다.

- W5500은 네트워크 처리를 칩이 떠안아 MCU가 측정/처리 루프에 집중할 수 있게 합니다.

- 이건 “전송을 하기 위해 이더넷을 쓴다”를 넘어서, DAQ의 안정성을 위해 이더넷 구현을 선택한 것으로 해석됩니다.

(추론임) 대안으로는 더 강력한 MCU/MPU를 써서 소프트웨어 스택을 감당하는 길도 있지만, 이 특허가 목표로 내세운 “저전력/장시간”과는 결이 다를 수 있습니다.

DAQ 관점에서의 장점 비교: 기존 접근 대비 차별 지점

- 센서 민감도만이 아니라, 전단–ADC–동기화–레퍼런스까지 포함한 ‘정밀 DAQ’로 설계

→ 약한 자기장 변화에서 ‘실제로 쓸 수 있는 데이터 품질’을 노립니다. - 다채널 어레이에 필수적인 ‘시간축 정렬’을 설계의 중심에 둠

→ 어레이 신호의 신뢰도를 결정하는 요소를 정확히 찌른 구성입니다. - WIZnet W5500 하드웨어 스택으로 전송부를 분리

→ MCU가 네트워크에 잠식되지 않도록 하여, DAQ 루프의 결정성과 전력 효율을 동시에 노립니다. - 이벤트 기반 전력/전송 모드 전환

→ “항상 풀파워”가 아니라 실제 현장 운용을 고려한 전략입니다.

이 시스템에서의 역할과 경계: “보조 수단”으로서의 위치

이 장치는 스스로 모든 결론을 내리는 시스템이라기보다, **현장에 설치되어 정밀 데이터를 안정적으로 수집·전송하는 ‘측정 인프라(DAQ 노드)’**에 가깝습니다.

즉, 최종 판정/분석/시각화는 상위(Host PC/플랫폼)에서 수행하고, 본 장치는 신뢰 가능한 원자료를 만들고 보존하는 역할에 집중합니다.

이 경계를 명확히 해야 “기기 단독으로 모든 문제 해결” 같은 과장이 아니라, 측정 시스템의 한 구성요소로 정확히 이해할 수 있습니다.

실패 비용이 가장 큰 판단 지점

가장 큰 실패 비용은 아날로그 전단에서 신호를 오염시키는 것입니다.

버퍼링/접지 분리/레퍼런스 안정/필터링/클럭 동기화가 무너져 신호가 한 번 망가지면, 이후 디지털 처리나 상위 분석으로 “원래의 지자기 이상”을 신뢰성 있게 복구하기 어렵습니다.

따라서 이 설계는 “후처리로 해결”이 아니라 “전단에서 망가지지 않게”에 비용을 투자한 구조로 보입니다.

특정 구성요소 제거 시 시스템 성격 변화

- Isolation(버퍼) 제거: 센서 로딩/임피던스 결합이 증가 → 노이즈/오프셋/이득 왜곡 리스크 상승

- 공통 저지터 클럭 제거: 채널 스큐 증가 → 어레이 분석 신뢰도 하락(가짜 이상 가능성 증가)

- W5500 제거(소프트웨어 스택 대체): MCU 부하/지터 증가 → 샘플링/전송 결정성 악화 가능, 전력/코드 복잡도 상승 가능

FAQ

- TMR 센서를 쓰면 무조건 정밀도가 올라가나요?

아닙니다. 센서 민감도는 출발점일 뿐이고, 실제 정밀도는 전단 노이즈, 레퍼런스 안정성, 접지/차폐, ADC 동기화까지 포함한 체인에서 결정됩니다. 이 특허는 그 “체인 전체”를 정밀 DAQ로 다룹니다. - 왜 3축을 굳이 ‘직교 배치’로 구성하나요?

지자기 이상은 방향 성분까지 포함하는 벡터 문제로 다뤄지는 경우가 많습니다. 직교 배치는 좌표계 변환과 보정의 기반이 되며, 어레이 해석 시 축 간 혼입을 줄이는 데 중요합니다. - 전압 팔로워(버퍼)는 왜 필요한가요? 그냥 증폭하면 안 되나요?

버퍼는 증폭과 목적이 다릅니다. 센서가 후단 회로에 의해 로딩되면 센서 출력 자체가 변형될 수 있고, 이로 인해 잡음과 오차가 늘어납니다. 버퍼는 이 결합을 끊어 “측정 대상”이 회로 상호작용으로 변질되는 것을 막습니다. - 계측 증폭기에서 ‘단일 저항 이득 설정’이 중요한 이유는 뭔가요?

어레이 시스템은 채널 수가 많아 채널 간 미세한 차이가 누적됩니다. 이득 설정에 저항 매칭 오차가 개입하면 채널 정합이 무너질 수 있습니다. 단일 저항 설정은 오차원을 구조적으로 줄이는 선택입니다. - 왜 24-bit ADC가 필요하나요? 샘플링 속도만 높이면 되지 않나요?

저레벨 자기장 변화를 보기 위해서는 “해상도”와 “대역 내 노이즈”가 중요합니다. 속도를 높이는 것만으로는 신호 대비 노이즈가 줄지 않을 수 있습니다. 이 특허는 delta-sigma ADC와 오버샘플링(예: OSR=8192)을 통해 유효 분해능과 잡음 특성을 관리하려고 합니다. - 채널 간 샘플링 편차(스큐)가 정말 그렇게 치명적인가요?

어레이는 여러 위치/축의 데이터를 동시에 비교하는 구조입니다. 채널이 시간축에서 어긋나면 공간 이상이 아니라 타이밍 불일치가 이상처럼 보일 수 있습니다. 그래서 공통 저지터 클럭으로 동기화에 투자합니다. - WIZnet W5500을 쓰는 이유가 단지 ‘이더넷이라서’인가요?

아닙니다. 이 특허에서 W5500은 “전송부”일 뿐 아니라, MCU가 소프트웨어 네트워크 스택으로 인해 DAQ 타이밍을 잃지 않도록 하는 설계 선택으로 볼 수 있습니다. 하드웨어 TCP/IP 오프로딩은 코드 복잡도와 지터 리스크를 줄이는 방향입니다. - 전력 관리(평상시 저전력/이상 시 풀동작)는 실제로 어떤 이점이 있나요?

장시간 야외 운용에서는 항상 최대 성능으로 돌리는 것이 불리할 수 있습니다. 이상 징후가 없을 때는 전송률·센서 수를 줄여 에너지를 아끼고, 이상이 감지되면 순간적으로 자원을 집중해 사건 구간을 포착하는 전략이 유효합니다. - 이 장치 하나로 “이상이 뭔지”까지 판단하나요?

기본적으로는 정밀 데이터를 만들고 올리는 DAQ 노드에 가깝습니다. 최종 분석/판정/시각화는 상위(호스트 PC/플랫폼)가 맡는 구조가 자연스럽습니다. 이 경계를 유지해야 시스템 과장이 아니라 역할 분담이 선명해집니다.

저자 정보 (Author Information)

출원/권리자(Assignee): Harbin Engineering University(哈爾濱工程大學)

공개된 자료 기준으로는 공학/해양/선박·방위 관련 연구 기반을 가진 공과대학 성격의 기관으로 알려져 있으나, 본 특허와 직접 연결된 상세 연구실/프로젝트 맥락은 본문에 제공된 정보만으로는 제한적입니다.

발명자(Inventors): 张晓峻, 陆鑫宇, 王爽, 陈明, 沈伦洋, 王×锋(본문 일부 글자 깨짐)

세부 이력/전공/역할 분담은 제공된 텍스트만으로 확인이 어렵습니다.