Development of an Integrated ROS Interface for a Time-of-Flight Measurement System of a LiDAR Sensor

Development of an Integrated ROS

Interface for a Time-of-Flight

Measurement System of a LiDAR Sensor

📘 Development of a ROS Interface for a LiDAR Sensor (Master's Thesis)

📌 Paper Overview

Title: Development of an Integrated ROS Interface for a Time-of-Flight Measurement System of a LiDAR Sensor

Author: Simão Pedro Torres Araújo (University of Minho, Portugal)

Year: 2021

Collaboration: Bosch Portugal & University of Minho

🎯 Research Objectives

Development of a LiDAR sensor system for autonomous vehicles:

Implementation of a high-precision Time-to-Digital Converter (TDC)

Integrated ROS (Robotic Operating System) interface

Full FPGA hardware implementation verification

🔬 Core Technologies

1. Double-sampling Gray TDC

Role: Measures the time from laser firing to reflected light detection (ToF)

Innovative Performance:

Resolution: 69 ps (1 cm depth resolution)

Precision: 59 ps

Power Consumption: 7 per channel LUTs, 20 Flip-flops, 1mW

73% resolution improvement over previous models

2. Software ROS Interface

Structure:

FPGA (TDC) → AXI → Zynq processor (Linux) → ROS Publisher → RVIZ visualization

Performance:

36,000 point cloud: 10.32 FPS

Power consumption: 2.087W

Disadvantages: Performance fluctuations due to OS overhead

3. Hardware ROS Interface (PoC)

Core: Utilizes the WIZ850io (W5500) network module

Structure:

FPGA (TDC) → FIFO → ROS Publisher (FPGA) → WIZ850io (SPI) → Ethernet

WIZ850io Configuration:

W5500 hardware TCP/IP stack

8 sockets (Sockets 0-2: for ROS communication)

SPI interface (30MHz)

IP: 192.168.1.10

🌟 Role of WIZ850io (W5500)

Key Contributions

TCP/IP stack hardware offload

Simultaneous operation of three TCP sockets required for ROS communication

No need to implement complex network protocols

System Simplification

No Linux OS required

No ARM processor required

ROS Publisher completed with FPGA only

Power Efficiency

84% reduction in overall system power

Suitable for industrial embedded systems

Bottlenecks

SPI interface Limitations:

30MHz operation (relatively slow)

Bit-by-bit serial transfer

FPS limited from 10.32 to 3.45

Author's improvement suggestions:

"Performance can be significantly improved by implementing TCP/IP directly on the FPGA or using a faster interface."

💡 Key Achievements

Academic Contributions

Development of a world-class TDC

Optimizing performance per resource

Ideal for multi-channel LiDAR sensors

Demonstrated full hardware ROS implementation

Implemented ROS node solely on FPGA without a processor

Reduced development time with WIZ850io

Industrial Applications

Bosch Automotive LiDAR Project

Academic Paper Published

==================

📘 LiDAR 센서용 ROS 인터페이스 개발 (석사학위 논문)

📌 논문 개요

제목: Development of an Integrated ROS Interface for a Time-of-Flight Measurement System of a LiDAR Sensor

저자: Simão Pedro Torres Araújo (University of Minho, 포르투갈)

연도: 2021년

협력: Bosch Portugal & University of Minho

🎯 연구 목표

자율주행 차량용 LiDAR 센서 시스템 개발:

- 고정밀 Time-to-Digital Converter (TDC) 구현

- ROS(Robotic Operating System) 인터페이스 통합

- FPGA 완전 하드웨어 구현 검증

🔬 핵심 기술

1. Double-sampling Gray TDC

역할: 레이저 발사 후 반사광 검출까지의 시간(ToF) 측정

혁신적 성능:

- 해상도: 69 ps (1cm 깊이 분해능)

- 정밀도: 59 ps

- 소비 자원: 채널당 7 LUTs, 20 Flip-flops, 1mW

- 기존 대비 해상도 73% 향상

2. 소프트웨어 ROS 인터페이스

구조:

FPGA(TDC) → AXI → Zynq 프로세서(Linux) → ROS Publisher → RVIZ 시각화성능:

- 36,000 포인트 클라우드: 10.32 FPS

- 전력 소비: 2.087W

- 단점: OS 오버헤드로 성능 변동

3. 하드웨어 ROS 인터페이스 (PoC)

핵심: WIZ850io (W5500) 네트워크 모듈 활용

구조:

FPGA(TDC) → FIFO → ROS Publisher(FPGA) → WIZ850io(SPI) → EthernetWIZ850io 설정:

- W5500 하드웨어 TCP/IP 스택

- 8개 소켓 (Socket 0-2: ROS 통신용)

- SPI 인터페이스 (30MHz)

- IP: 192.168.1.10

📊 소프트웨어 vs 하드웨어 비교

| 항목 | 소프트웨어 | 하드웨어(WIZ850io) |

|---|---|---|

| FPS | 10.32 (변동) | 3.45 (안정) |

| 프로세서 | 필요 | 불필요 ✅ |

| 전력 | 2.087W | 0.331W (-84%) |

| 안정성 | 낮음 | 매우 높음 |

| BRAM | 0 | 61 |

🌟 WIZ850io(W5500)의 역할

핵심 기여

- TCP/IP 스택 하드웨어 오프로드

- ROS 통신에 필요한 3개 TCP 소켓 동시 운영

- 복잡한 네트워크 프로토콜 구현 불필요

- 시스템 단순화

- Linux OS 불필요

- ARM 프로세서 불필요

- FPGA만으로 ROS Publisher 완성

- 전력 효율성

- 전체 시스템 전력 84% 감소

- 산업용 임베디드 시스템에 적합

병목 요인

SPI 인터페이스의 한계:

- 30MHz 동작 (상대적으로 느림)

- 비트 단위 직렬 전송

- FPS를 10.32 → 3.45로 제한

저자의 개선 제안:

"TCP/IP를 FPGA에 직접 구현하거나 더 빠른 인터페이스 사용 시 성능 대폭 향상 가능"

💡 주요 성과

학술적 기여

- 세계 최고 수준 TDC 개발

- 자원 대비 성능 최적화

- 다채널 LiDAR 센서에 이상적

- 완전 하드웨어 ROS 구현 입증

- 프로세서 없이 FPGA만으로 ROS 노드 구현

- WIZ850io로 개발 시간 단축

- 산업 적용

- Bosch 자동차 LiDAR 프로젝트

- 학술 논문 발표

이 133페이지 문서에서 15번의 W5500 언급 장면 - 12번은 5장에서 언급된다.

제1장: 서론 (Introduction) : 연구의 배경과 목적을 설정합니다.

내용: 자율 주행 및 정밀 매핑을 위한 LiDAR 센서의 중요성을 설명하고, 본 논문의 동기, 구체적인 연구 목표 및 방법론을 제시합니다.

제2장: 기술 현황 (State-of-the-Art): 본 연구와 관련된 기존 기술 및 이론적 배경을 검토합니다.

내용: LiDAR 센서의 원리, 시간-디지털 변환기(TDC), FPGA 구조, 그리고 로봇 운영 체제(ROS)에 대한 전반적인 개요와 최신 기술 동향을 다룹니다.

제3장: 이중 샘플링 그레이 TDC (Double-sampling Gray TDC): 본 연구에서 제안하는 핵심 하드웨어 아키텍처를 설명합니다.

내용: 해상도를 개선하기 위해 이중 샘플링 단계를 도입한 그레이 코드 오실레이터 기반 TDC의 설계, 구현 과정 및 테스트 결과(정밀도 및 해상도 등)를 상세히 기술합니다.

제4장: 소프트웨어 ROS 인터페이스 (Software ROS Interface): 프로세서에서 실행되는 소프트웨어 기반 인터페이스 구현을 다룹니다.

내용: PetaLinux를 이용한 임베디드 리눅스 이미지 생성, TDC 데이터 접근을 위한 리눅스 애플리케이션 개발, 그리고 RVIZ를 통해 데이터를 시각화하는 ROS 노드의 구현 과정을 설명합니다.

제5장: 하드웨어 ROS 인터페이스 (Hardware ROS Interface): 시스템 성능 최적화를 위한 하드웨어 기반 ROS 인터페이스 구현 및 분석을 다룹니다.

내용: ROS 네트워크 프로토콜을 분석하고, 이를 FPGA 하드웨어(Programmable Logic)로 이식하는 과정과 하드웨어에서 직접 메시지를 발행하는 방식의 성능(소비 전력 감소 및 성능 안정성)을 평가합니다.

5.1절은 "무엇을 어떻게 만들지 분석"하고, 5.2절은 "실제 하드웨어 로직으로 제작"하며, 5.3절은 "만들어진 결과물의 성능이 얼마나 좋아졌는지 검증"하는 단계입니다.

5.2.2절에서 12번, 5.2.3절에서 1번 언급된다.

처음 5번은 WIZ850io 소개하는 부분에서 언급되고, 6번째 언급은 아래에서 언급된다.

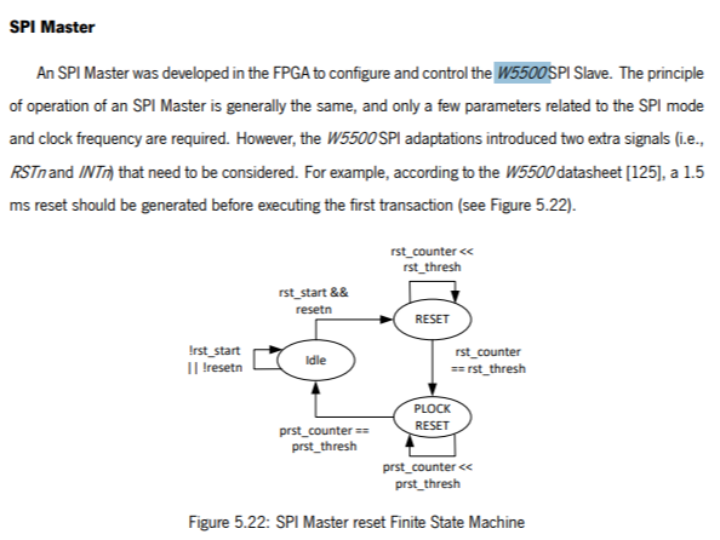

7번째와 8번째, 9번째 언급은 SPI Master 를 소개하면서 언급한다.

SPI Master는 FPGA가 외부 장치인 W5500(이더넷 컨트롤러)과 통신하기 위해 제어권(주도권)을 갖는 통신 주체를 말합니다.

이 논문에서는 FPGA 내부의 로직이 SPI Master가 됩니다. FPGA가 W5500(Slave)에게 "데이터를 보내라"거나 "이 데이터를 받아라"고 명령을 내리는 사령관 역할을 하는 것입니다.

10번째 언급은 Building the ROS publisher 절에서 나옵니다.

FPGA의 하드웨어 로직(Programmable Logic, PL)만으로 ROS 노드를 생성하고 데이터를 발행(Publish)하는 실제적인 구현 방법을 다루고 있습니다.

"임베디드 리눅스(OS) 도움 없이 FPGA 하드웨어만으로 어떻게 표준 ROS 통신 규약을 만족시키고, 실시간으로 Lidar 데이터를 전송할 수 있는가"에 대한 구체적인 기술적 해답을 담고 있습니다.

11번째 언급도 위의 연장선상에서 FPGA 와 W5500이 어떻게 데이타를 주고 받는지를 설명하는 부분에서 나옵니다.

12번째 언급은 실제 구현된 하드웨어가 어떻게 작동되는지를 설명하면서 언급되고 있습니다.

13~15번째 언급은 주석에 있다.

왜 하드웨어 부문에서 W5500을 이용했는가?

TCP/IP 프로토콜 스택을 하드웨어적으로 간단하게 구현하기 위함입니다. 상세한 이유는 다음과 같습니다.

1. TCP/IP 스택 구현의 단순화

복잡성 감소: ROS의 비동기 통신 시스템을 하드웨어(FPGA)로 옮기려면 TCP/IP 스택이 필수적입니다. 이를 FPGA 로직(HDL)으로 직접 모두 구현하는 것은 매우 복잡하고 시간이 많이 걸리는 작업입니다.

선택의 이유: 저자는 ROS 통신 구조를 분석하고 이해하는 데 집중하기 위해, 복잡한 TCP/IP 스택을 직접 설계하는 대신 이를 이미 칩 내부에 하드웨어로 구현하고 있는 W5500을 선택하여 구현 방식을 단순화했습니다.

2. 다중 소켓 지원 (ROS 통신 요구사항 충족)

필수 소켓 수: 하드웨어 기반의 ROS 퍼블리셔(Publisher)를 완전히 구동하려면 최소 3개의 소켓(클라이언트 1개, 서버 2개)이 필요합니다.

W5500의 성능: W5500은 최대 8개의 독립적인 소켓을 동시에 지원할 수 있어, ROS 노드 간의 통신(마스터 등록, 토픽 요청, 데이터 전송 등)에 필요한 다중 연결을 충분히 처리할 수 있습니다.

3. 하드웨어 리소스 효율성 및 독립성

프로세서 배제: W5500을 사용함으로써 기존의 소프트웨어 방식(PetaLinux 상의 ROS)과 달리 메인 프로세서(PS)의 도움 없이도 네트워크 통신이 가능해졌습니다.

하드웨어 컨트롤러: FPGA 내부에 W5500을 제어하기 위한 SPI 마스터 FSM(유한 상태 머신)을 설계하여 장치를 제어하도록 함으로써 시스템의 하드웨어 독립성을 확보했습니다.

4. 개념 증명(PoC) 목적

실행 가능성 확인: 이 연구는 ROS 인터페이스의 하드웨어 이식이 가능하다는 것을 보여주는 '개념 증명(Proof of Concept)' 단계에 중점을 두었습니다. 따라서 가장 효율적이고 안정적으로 네트워크 기능을 추가할 수 있는 수단으로 W5500 기반의 WIZ850io 모듈을 활용한 것입니다.

요약하자면, W5500은 FPGA에서 ROS 통신에 필수적인 TCP/IP 기능을 하드웨어적으로 쉽고 빠르게 통합할 수 있게 해주어, 연구의 핵심인 ROS 인터페이스 설계에 더 집중할 수 있게 해주는 도구로 사용되었습니다.