How Do You Build an IPv4/IPv6 Gateway on STM32 Using W6100?

How Do You Build an IPv4/IPv6 Gateway on STM32 Using W6100?

How Do You Build an IPv4/IPv6 Gateway on STM32 Using W6100?

Register-Level TCP Behavior and Dual-Stack Gateway Architecture Explained

(STM32와 W6100으로 IPv4/IPv6 게이트웨이를 설계하면 무엇이 달라지는가?)

Summary (40–60 words)

This article explains how to design an embedded IPv4/IPv6 gateway using an STM32 microcontroller and the WIZnet W6100 Ethernet controller. By analyzing register-level TCP behavior, socket lifecycle management, and dual-stack data flow, it shows how hardware TCP/IP offloading enables reliable, future-proof gateway implementations for industrial and IoT systems.

1. Why IPv4/IPv6 Gateways Matter Now

IPv6 is no longer theoretical.

In many regions, networks are already:

IPv6-only internally

Dual-stack at the edge

Gradually deprecating IPv4

Embedded systems that only support IPv4 risk:

Limited deployability

Complex network workarounds

Shortened product lifetime

An IPv4/IPv6 gateway allows embedded devices to:

Communicate with both legacy and modern networks

Bridge protocol generations safely

Remain deployable for many years

2. Why STM32 + W6100 Is a Strong Gateway Platform

STM32 Role

Application logic

Protocol translation logic

Data processing and control

W6100 Role

Hardware TCP/IP offloading

Native IPv4 + IPv6 dual-stack

Deterministic socket behavior

STM32 handles “what the gateway does.”

W6100 guarantees “how packets move correctly.”

This separation is critical for gateway reliability.

3. High-Level Gateway Architecture

Dual-Stack Gateway Model

Key architectural decision:

The gateway logic lives above the TCP socket layer

W6100 is responsible only for transport correctness

4. W6100 Dual-Stack Design (What Makes It Different)

Unlike W5500, the W6100 natively supports IPv6, including:

IPv6 addressing

IPv6 TCP/UDP checksum handling

Dual-stack socket operation

From the firmware perspective:

IPv4 and IPv6 sockets share the same lifecycle model

Only address format and socket configuration differ

This dramatically simplifies gateway design.

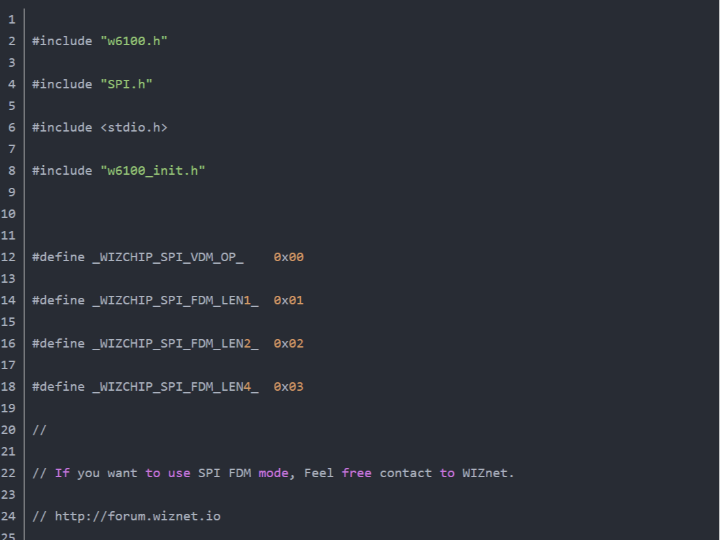

5. Socket Initialization for IPv4 and IPv6

Common Initialization Steps

Configure MAC address

Configure network parameters

IPv4: IP, gateway, subnet

IPv6: address, prefix, gateway

Allocate TX/RX buffer sizes

Open socket in TCP mode

The socket state machine remains identical for both stacks.

6. Register-Level TCP Behavior in Gateway Operation

TCP Client Establishment (Conceptual)

At this point:

W6100 performs TCP handshake

STM32 does not process SYN/ACK/FIN packets

This is essential for deterministic behavior.

7. Data Flow Through the Gateway

RX Path (Inbound Side)

TX Path (Outbound Side)

This process is identical for IPv4 and IPv6.

8. Why Register-Level Understanding Is Critical

In gateway applications:

Traffic is continuous

Sockets stay open long-term

Buffer mismanagement accumulates errors

Common gateway failures include:

One side stops receiving data

TCP window collapse

Silent connection stalls

These almost always trace back to:

RX pointer not advanced

SEND issued without correct TX pointer update

Not to TCP itself.

9. Gateway-Specific TCP Lifecycle Considerations

Unlike short-lived clients, gateways must:

Keep sockets open for long durations

Handle reconnects gracefully

Recover from network interruptions

W6100’s fixed socket model helps by:

Exposing socket states clearly

Avoiding dynamic memory allocation

Making failure detection explicit

10. Performance and Determinism

Throughput

Limited by:

SPI clock speed

Buffer configuration

Application processing

Not limited by:

TCP/IP stack complexity

Latency

Deterministic within the device

Dominated by network path

This predictability is essential for gateway reliability.

11. Common Gateway Failure Modes

❌ IPv4 side works, IPv6 side stalls

Cause:

IPv6 socket configured but RX buffer not drained

❌ Gateway works initially, then freezes

Cause:

RECV command omitted during long operation

❌ High CPU load observed

Cause:

Firmware reimplementing TCP logic unnecessarily

Correct register-level handling avoids all of these.

12. Why W6100 Is Well-Suited for Industrial Gateways

Native IPv6 support

Hardware TCP/IP offloading

Deterministic socket model

Long-term stability

These characteristics align with:

Industrial controllers

Building automation gateways

Energy and infrastructure systems

13. Key Takeaway

Using W6100, an STM32-based IPv4/IPv6 gateway becomes a controlled socket and buffer management problem—not a complex dual-stack networking problem.

When register-level TCP behavior is understood:

Gateway logic stays simple

Dual-stack operation is reliable

Systems remain future-proof

FAQ (Engineer-Focused)

Q1. Does W6100 translate IPv4 to IPv6 automatically?

No. Translation logic runs on STM32; W6100 handles transport.

Q2. Is TCP behavior different between IPv4 and IPv6?

No. The socket lifecycle is the same.

Q3. Can this gateway run under RTOS?

Yes, with proper SPI protection.

Q4. Is UDP also supported?

Yes, equally for IPv4 and IPv6.

Q5. Is this suitable for production gateways?

Yes, with proper protocol logic on STM32.

Source

CSDN article: ic2121 (129611502)

WIZnet W6100 Datasheet

IPv6 Architecture (RFC 8200)

Tags

W6100, WIZnet, STM32, IPv6 Gateway, Dual Stack, TCP Socket, Embedded Ethernet, Industrial IoT

🇰🇷 한국어 번역 (1:1 Full Translation)

STM32와 W6100으로 IPv4/IPv6 게이트웨이를 설계하면 무엇이 달라지는가?

레지스터 수준 TCP 동작으로 이해하는 듀얼 스택 게이트웨이 구조

요약

본 문서는 STM32 마이크로컨트롤러와 WIZnet W6100 이더넷 컨트롤러를 사용해 IPv4/IPv6 듀얼 스택 게이트웨이를 설계하는 구조를 설명한다. TCP 소켓 초기화, 레지스터 기반 데이터 흐름, 게이트웨이 동작 특성을 분석함으로써 하드웨어 TCP/IP 오프로딩이 안정적인 듀얼 스택 구현을 어떻게 가능하게 하는지 보여준다.

1. IPv4/IPv6 게이트웨이의 필요성

IPv6는

이미 현실이다.

2. 시스템 아키텍처

3. 소켓 초기화와 생명주기

IPv4와 IPv6는

동일한 소켓 모델을 사용한다.

4. 데이터 흐름

RX 포인터와

TX 포인터가 핵심이다.

5. 흔한 오류

RECV 누락

포인터 미갱신

6. 핵심 메시지

W6100은 듀얼 스택을 복잡한 문제에서 관리 가능한 문제로 바꾼다.

태그

W6100, STM32, IPv6 게이트웨이, 듀얼 스택, 임베디드 이더넷