How Should W5500 Registers Be Initialized for Reliable Ethernet Communication?

This article explains the correct register initialization sequence of the WIZnet W5500 Ethernet controller and highlights common debugging pitfalls.

How Should W5500 Registers Be Initialized for Reliable Ethernet Communication?

Correct Initialization Sequence, Common Pitfalls, and Debugging Insights

(W5500 레지스터는 어떤 순서로 초기화해야 안정적인 이더넷 통신이 가능한가?)

Summary (40–60 words)

This article explains the correct register initialization sequence of the WIZnet W5500 Ethernet controller and highlights common debugging pitfalls. By understanding how SPI access, common registers, socket registers, and buffer allocation interact, developers can build stable, platform-agnostic TCP/UDP firmware without relying on complex software TCP/IP stacks.

1. Why W5500 Initialization Order Matters

The W5500 integrates a full hardware TCP/IP stack, but it is not a “plug-and-play” device.

From the MCU’s perspective, Ethernet only works correctly if:

Registers are initialized in the correct order

Buffer sizes are configured before socket use

Socket commands are issued only in valid states

Many networking issues attributed to “TCP bugs” are actually caused by incorrect initialization.

On W5500, the initialization sequence defines the behavior of the entire network stack.

2. Platform-Agnostic Architecture Overview

The following structure applies to any MCU (ARM, RISC-V, AVR, RP2040, etc.):

Key point:

No software TCP/IP stack exists on the MCU

All networking behavior emerges from register configuration

3. Correct W5500 Register Initialization Sequence

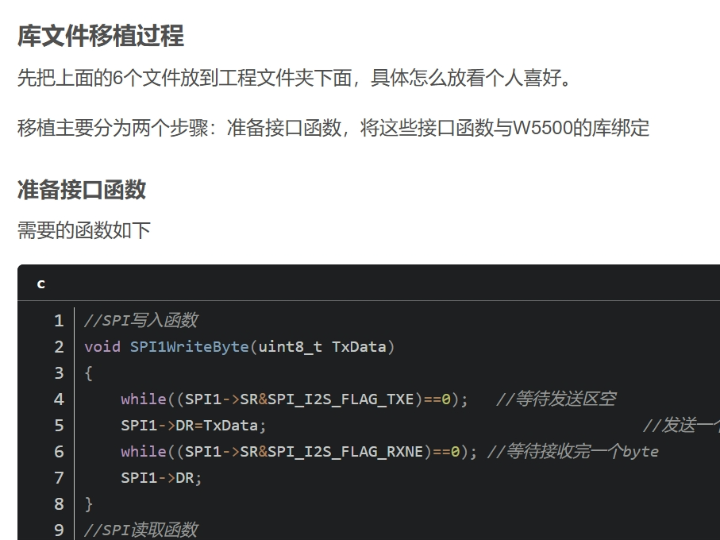

Step 1: SPI and Reset

Before touching any register:

Initialize SPI peripheral

Toggle W5500 RESET pin

Wait for internal PHY stabilization

Failing here leads to random register reads.

Step 2: Common Register Configuration

Configure global network parameters first:

MAC address

IP address

Subnet mask

Gateway address

These registers define how the W5500 participates in the network.

⚠️ Do not open sockets before setting common registers.

Step 3: TX/RX Buffer Size Allocation

W5500 provides:

16 KB total TX buffer

16 KB total RX buffer

Shared across 8 sockets

Typical allocation example:

Socket 0: 4 KB TX / 4 KB RX

Socket 1–3: smaller buffers

Remaining sockets disabled

This step must be completed before socket activation.

Step 4: Socket Register Initialization

For each socket in use:

Set socket mode (TCP / UDP)

Configure local port

Set destination IP/port (client mode)

At this stage, the socket is configured but inactive.

Step 5: Socket Command Execution

Issue socket commands in valid order:

OPEN

LISTEN (server) or CONNECT (client)

The W5500 will now manage the TCP/UDP state machine internally.

4. Why This Sequence Works

This order respects internal dependencies:

Network identity must exist before communication

Buffers must exist before data movement

Sockets must be configured before activation

Violating these rules causes undefined behavior that is difficult to debug.

5. Common Debugging Pitfalls

❌ Pitfall 1: Socket Opens but Cannot Communicate

Cause:

Buffers not allocated before socket open

Symptom:

CONNECT succeeds, but SEND fails silently

❌ Pitfall 2: RX Size Shows Data, But recv() Returns Nothing

Cause:

RX read pointer not updated

RECV command not issued

❌ Pitfall 3: Random Connection Drops

Cause:

SPI transactions split across CS boundaries

Interrupted multi-byte register access

Rule: One SPI frame = one CS assertion.

❌ Pitfall 4: Socket Stuck in CLOSE_WAIT

Cause:

Firmware never drains RX buffer

RECV command omitted

6. Debugging Strategy (Engineer Approach)

When debugging W5500 issues, check in this order:

SPI waveform (logic analyzer)

Common register values

Buffer size registers

Socket status register transitions

TX/RX pointer movement

Do not start by debugging TCP logic.

7. Why W5500 Simplifies Platform-Agnostic Firmware

Because W5500:

Implements TCP/UDP in hardware

Uses memory-mapped registers

Exposes buffers explicitly

The same driver logic works on:

Bare-metal systems

RTOS-based firmware

Different MCU architectures

Only the SPI driver changes.

8. TCP and UDP Become Register Problems

Once initialization is correct:

TCP reliability is automatic

UDP framing is handled in hardware

Firmware logic becomes deterministic

This is why W5500 is widely used in industrial and long-life products.

9. Practical Takeaways

Initialization order is non-negotiable

Most bugs are configuration bugs

Correct register understanding eliminates TCP mysteries

10. Key Takeaway

On W5500, reliable Ethernet communication starts with a correct register initialization sequence—not with application code.

Engineers who master this sequence can build stable, portable TCP/UDP firmware across platforms with minimal complexity.

FAQ (Engineer-Focused)

Q1. Can I skip buffer configuration if I use only one socket?

No. Buffers must always be allocated explicitly.

Q2. Does W5500 auto-initialize registers on reset?

Only partially. Network and socket configuration is the MCU’s responsibility.

Q3. Are these rules MCU-specific?

No. They apply to all platforms.

Q4. Is this relevant for both TCP and UDP?

Yes. Both rely on the same buffer and SPI model.

Q5. Why is debugging easier than software TCP/IP?

Because behavior maps directly to register states.

Source

CSDN article (YinShiJiaW)

WIZnet W5500 Datasheet

Tags

W5500, WIZnet, Register Initialization, Ethernet Debugging, SPI Driver, TCP UDP, Embedded Ethernet, Platform-Agnostic Firmware

🇰🇷 한국어 번역 (1:1 Full Translation)

W5500 레지스터는 어떤 순서로 초기화해야 안정적인 이더넷 통신이 가능한가?

올바른 초기화 순서, 디버깅 포인트, 공통 오류 분석

요약

본 문서는 WIZnet W5500 이더넷 컨트롤러의 레지스터 초기화 순서와 대표적인 디버깅 오류를 설명한다. SPI 접근, 공통 레지스터, 버퍼 할당, 소켓 초기화의 관계를 이해함으로써, 플랫폼에 종속되지 않는 안정적인 TCP/UDP 펌웨어 구현이 가능함을 보여준다.

1. 초기화 순서가 중요한 이유

W5500은 하드웨어 TCP/IP를 제공하지만

초기화 순서를 지키지 않으면 정상 동작하지 않는다.

2. 플랫폼 독립적 구조

3. 올바른 초기화 단계

SPI 및 리셋

공통 레지스터 설정

TX/RX 버퍼 할당

소켓 레지스터 설정

소켓 명령 실행

4. 대표적인 오류 원인

버퍼 미할당

RX 포인터 미갱신

CS 타이밍 오류

CLOSE_WAIT 정체

5. 디버깅 순서

TCP가 아니라

레지스터부터 확인하라.

6. 핵심 메시지

W5500 이더넷의 안정성은 초기화 순서에서 시작된다.

태그

W5500, WIZnet, 레지스터 초기화, 이더넷 디버깅, 임베디드 TCP/IP