How Do W5500 Registers, Buffers, and SPI Timing Enable TCP Networking on RT-Thread?

This article explains how WIZnet W5500 register architecture, TX/RX buffer usage, and SPI chip-select timing work together to enable stable TCP communication un

How Do W5500 Registers, Buffers, and SPI Timing Enable TCP Networking on RT-Thread?

(W5500의 레지스터·버퍼·SPI 타이밍은 RT-Thread에서 TCP 네트워크를 어떻게 가능하게 할까?)

Summary (40–60 words)

This article explains how WIZnet W5500 register architecture, TX/RX buffer usage, and SPI chip-select timing work together to enable stable TCP communication under RT-Thread. By understanding how the RTOS driver maps sockets to hardware buffers and synchronizes SPI access, beginners can build reliable embedded Ethernet applications without implementing a software TCP/IP stack.

1. Why W5500 + RT-Thread Is a Common Combination

RT-Thread is widely used in embedded systems because it provides:

Multithreading

IPC mechanisms (semaphores, mutexes)

Device driver abstraction

Lightweight TCP/IP integration options

When combined with WIZnet W5500, developers gain an additional advantage:

TCP/IP processing is handled in hardware, not by the RTOS.

This makes W5500 particularly suitable for RT-Thread-based systems where deterministic behavior and low CPU usage are important.

2. Overall Architecture: RT-Thread + W5500

System Architecture Diagram

The key idea is that RT-Thread threads do not handle TCP/IP internals.

They interact with W5500 through register operations.

3. W5500 Register and Buffer Organization (Beginner View)

The W5500 memory map is divided into logical blocks, not flat memory.

3.1 Common Register Block

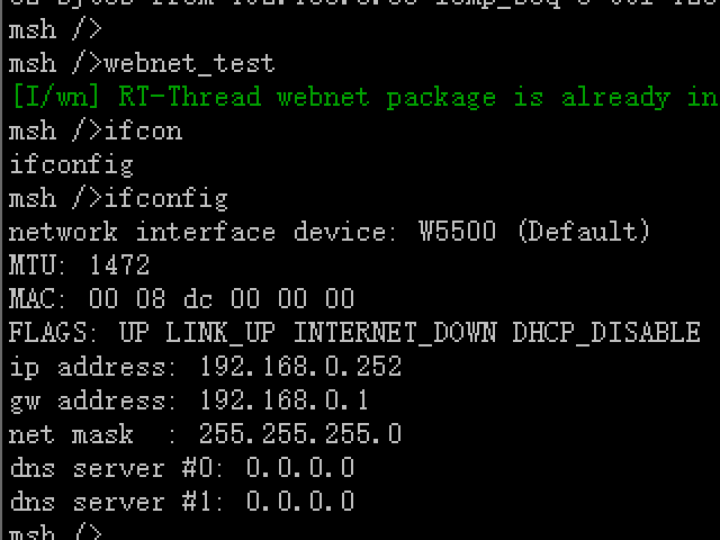

This block defines global network identity:

MAC address

IP address

Subnet mask

Gateway

PHY configuration

Without correctly configuring these registers, no TCP socket can function.

3.2 Socket Register Blocks (8 Identical Sets)

Each socket has its own register set:

Mode (TCP / UDP)

Source port

Destination IP / port

Status and interrupt flags

RT-Thread typically assigns one thread or one connection per socket, making the mapping intuitive.

3.3 TX / RX Buffer Memory

The W5500 provides:

16 KB TX buffer (shared)

16 KB RX buffer (shared)

Configurable per socket at initialization

Important beginner concept:

TX/RX buffers are accessed only via SPI with correct block selection — they are not MCU RAM.

4. SPI Access Model and CS Timing

W5500 SPI Transaction Structure

In Variable Length Data Mode (VDM):

Data length is defined by CS LOW duration

Releasing CS early aborts the transaction

Why CS Timing Matters in RT-Thread

RT-Thread is multi-threaded.

This introduces two risks:

Multiple threads accessing SPI simultaneously

CS toggled before data transfer completes

To avoid this:

SPI access is protected by mutexes

CS is asserted and deasserted inside the driver, not in application threads

This ensures atomic SPI transactions.

5. How RT-Thread Synchronizes with W5500

SPI Synchronization Flow

This design guarantees:

No race conditions

Correct SPI framing

Stable TCP behavior

6. TCP Communication Flow with W5500 on RT-Thread

Conceptual TCP Client Flow

🧩 Conceptual flow (educational)

Each step is implemented by writing or reading W5500 registers, not by running a TCP stack in software.

7. Why This Design Is Beginner-Friendly

Beginners often struggle with:

TCP state machines

Retransmission logic

Memory-heavy network stacks

With W5500:

TCP complexity is hidden in hardware

RT-Thread manages concurrency

Developers focus on data flow and application logic

This dramatically shortens development time.

8. Reliability Advantages in RTOS Environments

Deterministic Behavior

No TCP processing jitter in threads

Hardware-managed retransmission

Predictable timing

Reduced Memory Pressure

No LwIP or similar stack required

More RAM available for application tasks

This makes W5500 ideal for industrial and long-running systems.

9. Common Pitfalls and How Understanding Helps

| Pitfall | Root Cause | Solution |

|---|---|---|

| TCP connect fails | Wrong common registers | Verify MAC/IP setup |

| Random SPI errors | CS timing broken | Driver-level CS control |

| Data corruption | Buffer offset error | Understand TX/RX mapping |

| RTOS deadlock | SPI not mutex-protected | Use RT-Thread IPC |

Understanding registers + buffers + SPI timing prevents these issues.

10. Key Takeaway

On RT-Thread, W5500 turns TCP networking into a register-driven, deterministic hardware operation.

Once developers understand:

Register blocks

Buffer usage

SPI and CS timing

TCP becomes configuration and data movement, not protocol implementation.

FAQ

Q1. Does RT-Thread still need a TCP/IP stack?

No. W5500 handles TCP/IP in hardware.

Q2. Why is CS timing critical in RTOS systems?

Because multiple threads may access SPI; incorrect CS breaks transactions.

Q3. Can multiple TCP sockets run concurrently?

Yes. W5500 supports 8 hardware sockets.

Q4. Is this suitable for industrial products?

Yes. The design emphasizes stability and predictability.

Q5. Is this approach beginner-friendly?

Yes. Complexity is front-loaded into hardware, not firmware.

Source

CNBlogs article (W5500 + RT-Thread register and SPI discussion)

WIZnet W5500 datasheet

Tags

W5500, WIZnet, RT-Thread, SPI Ethernet, Register Architecture, TCP Client, Embedded Ethernet, Industrial IoT

🇰🇷 한국어 번역 (1:1 Full Translation)

W5500의 레지스터·버퍼·SPI 타이밍은 RT-Thread에서 TCP 네트워크를 어떻게 가능하게 할까?

요약

본 문서는 WIZnet W5500의 레지스터 구조, TX/RX 버퍼 사용 방식, SPI 칩 선택(CS) 타이밍이 RT-Thread 환경에서 TCP 통신을 어떻게 안정적으로 구현하는지 설명한다. RTOS 드라이버가 하드웨어 소켓과 SPI 접근을 어떻게 동기화하는지 이해하면 초보자도 안정적인 이더넷 애플리케이션을 개발할 수 있다.

1. W5500 + RT-Thread 조합이 널리 사용되는 이유

RT-Thread는 멀티스레드와 IPC를 제공하며,

W5500은 TCP/IP를 하드웨어로 처리한다.

즉, RTOS와 네트워크 스택의 부담이 분리된다.

2. 전체 아키텍처 개요

3. W5500 레지스터와 버퍼 구조

공통 레지스터

MAC, IP, 게이트웨이 설정 담당

소켓 레지스터

TCP/UDP 채널 제어

TX/RX 버퍼

송신·수신 데이터 저장

4. SPI 접근과 CS 타이밍

VDM 모드에서는:

CS가 데이터 길이를 정의

CS 오류 = 트랜잭션 오류

RT-Thread에서는 드라이버가 CS를 제어한다.

5. RT-Thread에서의 동기화 흐름

6. TCP 통신 흐름 (개념)

7. 초보자 친화적인 이유

TCP 스택 구현 불필요

RTOS 동기화 제공

하드웨어가 복잡성 처리

8. 산업용 신뢰성

결정적 타이밍

낮은 CPU 부하

장시간 안정 동작

9. 핵심 메시지

RT-Thread에서 W5500은 TCP를 “하드웨어 레지스터 작업”으로 바꾼다.

태그

W5500, WIZnet, RT-Thread, SPI 이더넷, TCP 통신, 임베디드 네트워크