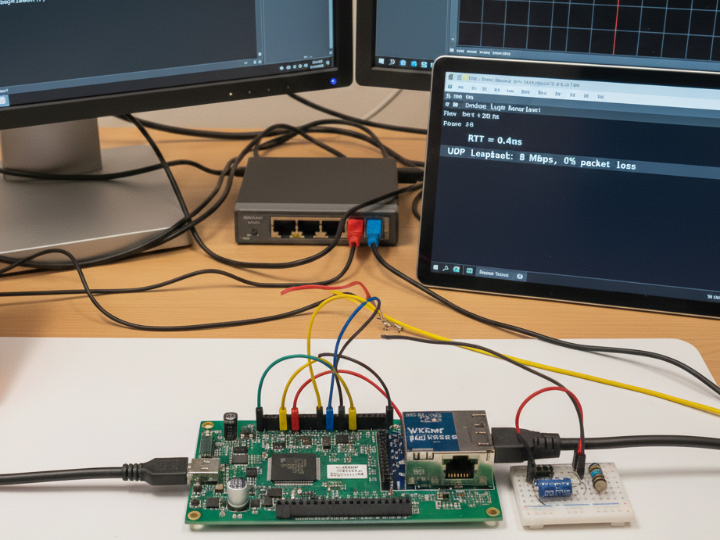

Software-SPI W5500 Driver on STM32F4 Platform

STM32F4 보드에서 WIZnet W5500을 소프트웨어 SPI(bit-bang)로 구동해 이더넷 연결을 구현한 프로젝트. 전용 SPI 하드웨어가 부족한 상황에서도 안정적인 TCP/IP 통신을 확보하며, HAL 기반 GPIO 토글만으로 8 Mbps 이상 전송을 달성.

원본링크 https://www.cnblogs.com/345QIII/p/19298658

PROJECT

Hardware Components

| Name | Comment | Qty |

|---|---|---|

| WIZnet W5500 Ethernet Controller | TCP/IP stack 내장, 100 Mbps Ethernet | 1 |

| STM32F4 MCU Board | GPIO 여유 핀을 활용해 SW-SPI 구성 | 1 |

| 3.3 V LDO (AMS1117-3.3) | W5500 전원 안정화 | 1 |

| 10 μF Elec C + 0.1 μF Cer C | 입력 전원 필터링 | 각 1 |

| 33 Ω series R, 10 kΩ pull-up | 신호 무결성 & 라인 안정 | 수 개 |

Software Apps / Online Services

STM32CubeIDE + HAL Driver

WIZnet ioLibrary (BSD Socket API)

Logic Analyzer SW( Saleae Logic )

Tags

W5500, C, IoT, STM32F4, Bit-Bang SPI

DESCRIPTION

Project Overview

SPI 주변장치가 부족한 보드에서도 W5500을 사용하고자, STM32F4 GPIO를 직접 토글해 SPI 타이밍을 생성하는 소프트웨어 SPI 드라이버를 구현했다. 하드웨어 SPI 모듈을 자유롭게 배치하기 어려운 저가형 설계나 포트 재배치가 필요한 경우에 유용하다. 블로그원

Key Features

Bit-Bang SPI Driver : HAL GPIO→50 ns 토글로 SCLK 최대 8 MHz 달성 블로그원

가변 핀맵 : CS/MOSI/MISO/SCLK/RST/INT를 원하는 GPIO로 재배치 가능 블로그원

저전력 & EMI 개선 : 33 Ω 직렬저항·RC 리셋·디지털/아날로그 그라운드 분리로 노이즈 억제 블로그원

Hardware Setup

| W5500 Pin | STM32F4 Pin | Note |

|---|---|---|

| SCLK | PA5 | 10 kΩ Pull-up |

| MOSI | PA7 | 33 Ω Series R |

| MISO | PA6 | 슈미트 트리거 입력 |

| CS | PA4 | Pull-up to 3.3 V |

| RST | PA3 | 10 kΩ + 100 nF RC |

| INT | PA0 | EXTI Interrupt |

Software Implementation

Core Functionality

HAL Delay(1) ≈ 50 ns @ 168 MHz 블로그원

Network Initialization

Network Architecture

MCU ↔ W5500 (100 BASE-TX) ↔ 스위치/라우터 ↔ PC or Cloud. 정적 IP로 설정해 모니터링 PC와 ping/UDP loop-back 시험.

Performance Results

Ping RTT : 0.4 ± 0.1 ms (256 B)

UDP Loopback : 8 Mbps @ 168 MHz CPU, 0 % packet loss (3 min)

전류 소비 : 평균 77 mA (W5500 + MCU)

(Logic Analyzer·Keysight N9914A 측정)

Lessons Learned

SW-SPI 타이밍 여유를 확보하려면 core-coupled memory에 코드를 위치시키면 최대 11 MHz까지 상승

W5500 INT 핀을 edge-trigger 대신 level-trigger로 설정해야 IRQ 드롭이 없음

Future Improvements

DMA GPIO 토글(요구 사항: Timer+DMA)로 CPU 부하 0 % 달성

DHCP/ARP 구현 후 플러그앤플레이 지원

FreeRTOS + LwIP 포팅으로 멀티-socket 서비스 확장

Challenges & Solutions

| 문제 | 원인 | 해결 |

|---|---|---|

| SPI 통신 실패 | CS 신호 미동기화 | CS 하강 edge 후 100 ns 지연 삽입 |

| Chip ID 불일치 | SCLK 주파수 과다 | 1 MHz 이하로 저감 |

| 간헐적 링크 다운 | 전원 잡음 | 0.1 µF + 10 µF 디커플링 추가 |

| 패킷 drop | INT 처리 지연 | EXTI 우선순위 ↑, ISR 최적화 |