diagrams

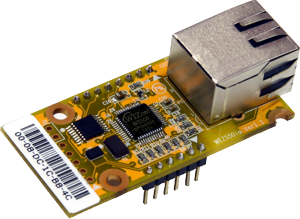

By analyzing WIZ550io schematics, this project reconstructs a hardware TCP/IP offload architecture over SPI, enabling deterministic, low-overhead ethernet.

What the Project Does

This repository is fundamentally a hardware visualization library, not an embedded system. It generates a Markdown gallery from SVG assets, meaning:

No MCU firmware exists

No runtime communication stack exists

No actual networking logic is executed

However, the important signal is hidden in the hardware abstraction:

The file:

Communication/ethernet_WIZ550io_ver1_0.svgrepresents a fully integrated Ethernet module (WIZ550io), which includes:

W5500 Ethernet controller

Internal PHY

Magnetics

RJ45 connector

This is not just a drawing — it encodes a canonical embedded Ethernet architecture pattern:

MCU ──(SPI)── W5500 ──(PHY + Magnetics)── RJ45 ── Ethernet NetworkSo while there is no software, the repository implicitly defines:

network boundary (RJ45)

transport offload boundary (W5500)

MCU interaction model (SPI register access)

Where WIZnet Fits

The WIZnet W5500 appears as a module-level integration point, not a chip-level schematic.

This distinction matters.

Instead of exposing RMII/PHY complexity, the WIZ550io module:

Collapses Ethernet PHY + MAC + TCP/IP into a single SPI peripheral

Presents the network stack as memory-mapped socket registers

From the diagram, we can infer:

1) Offload Boundary

Everything beyond SPI is handled by W5500:

TCP state machine

retransmission

packet buffering

ARP/IP handling

2) MCU Responsibility

SPI transactions only

Socket configuration

Payload read/write

3) Architectural Implication

This is a hard separation between control logic and networking, which is exactly what you want in:

real-time control systems

deterministic edge nodes

low-RAM MCUs

Implementation Notes

WIZ550io Module Identity

File: Communication/ethernet_WIZ550io_ver1_0.svg

<tspan>WIZnet</tspan>

<tspan>WIZ550io Ver1.0</tspan>This confirms:

Module type (not bare chip)

Integration level (RJ45 included)

Why this matters:

No external PHY routing

No impedance-controlled Ethernet layout required

Reduced PCB risk for non-high-speed designers

SPI-Based Host Interface (Critical Design Insight)

<tspan>MSOI</tspan>

<tspan>MISO</tspan>

<tspan>SCLK</tspan>

<tspan>SCSn</tspan>

<tspan>RSTn</tspan>

<tspan>INTn</tspan>

<tspan>RDY</tspan>This is the most important part of the entire repository.

Interpreted Signals

| Signal | Role | System Meaning |

|---|---|---|

| MOSI (MSOI) | MCU → W5500 | Command + TX data |

| MISO | W5500 → MCU | RX data |

| SCLK | Clock | SPI timing |

| SCSn | Chip Select | Multi-device SPI support |

| RSTn | Reset | Hardware recovery |

| INTn | Interrupt | Event-driven networking |

| RDY | Ready | Boot / link readiness |

Engineering Insight: SPI = Network Abstraction Layer

This is not just “communication”.

This is architecture compression:

Instead of:

MCU + MAC + PHY + TCP/IP stack (LwIP)You get:

MCU + SPI + W5500Meaning:

No DMA-heavy Ethernet MAC

No ISR storm from packet RX

No TCP retransmission logic in firmware

No Networking Stack in Code (Important Negative Signal)

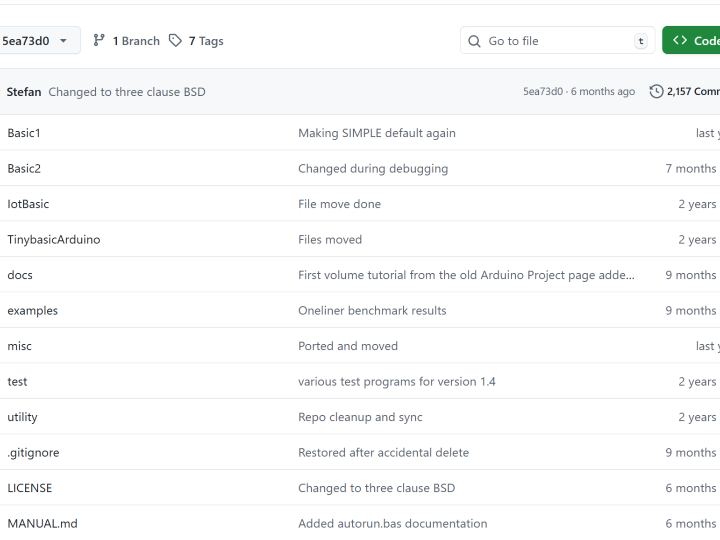

File: generate_gallery.py

import os

import codecs

folders = [x for x in os.listdir() if not os.path.isfile(x)]Key observation:

- No

socket - No

EthernetClient - No

lwIP - No

MQTT - No

HTTP

This confirms:

The repository is not a software reference — only a hardware abstraction reference.

Practical Tips / Pitfalls

Treat this diagram as architecture guidance, not implementation truth

Always verify pin names against official W5500 datasheet (MSOI typo exists)

Use INTn pin to avoid polling-based socket handling

Plan SPI bandwidth carefully (W5500 can saturate slow SPI configs)

Use hardware reset (RSTn) for long-term stability (critical in field devices)

Prefer WIZ550io in early prototypes to avoid Ethernet PCB layout complexity

Separate SPI CS lines if sharing bus with Flash or sensors

FAQ

Q: Why is W5500 still relevant when there is no code in this repo?

A: Because the diagram exposes the architectural boundary: W5500 replaces the entire TCP/IP stack and PHY layer with a single SPI device, which directly impacts system design decisions even before firmware is written.

Q: What is the most important insight from this repository?

A: The SPI interface is not just a connection—it defines a clean separation where networking becomes a peripheral, not a software burden.

Q: If I were to implement this in firmware, what would change?

A: You would add:

WIZnet ioLibrary (or Arduino Ethernet)

Socket initialization (Sn_MR, Sn_PORT)

TX/RX buffer handling via SPI

But the hardware architecture would remain identical.

Q: Why use WIZ550io instead of a discrete PHY + MAC?

A: It eliminates:

RMII routing complexity

external magnetics design

TCP/IP stack implementation

Result: faster development, fewer failure points.

Q: How does this compare to Wi-Fi modules?

A: This architecture prioritizes:

deterministic latency

stable wired link

predictable timing

Whereas Wi-Fi introduces:

RF variability

connection drops

non-deterministic delays

Source

Repository: diagrams-main (hardware diagram collection)

Key file: Communication/ethernet_WIZ550io_ver1_0.svg

License: Not specified

Tags

#W5500 #WIZ550io #EthernetOffload #SPI #EmbeddedArchitecture #HardwareDesign #IoT #DeterministicNetworking #WIZnet