Real-time Distributed LED Wall Control System

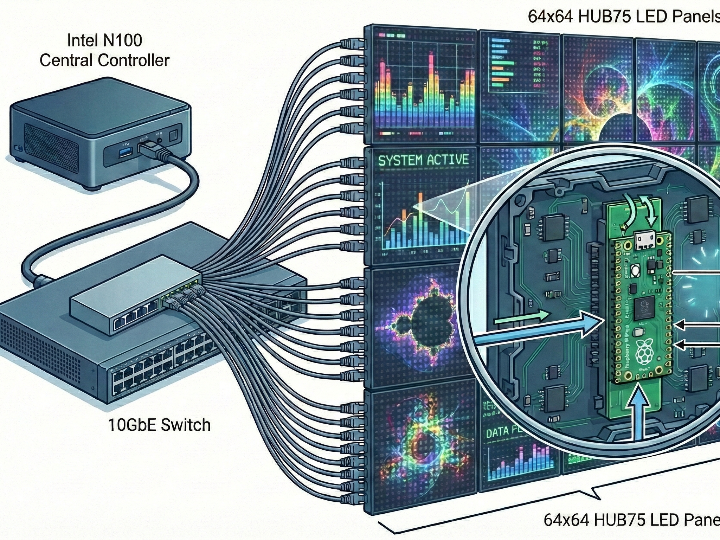

Intel N100 PC sends video to 800 LED panels via 10GbE. Each panel has a Pico controller. Zero-copy code ensures real-time sync on the 20m2 display wall.

1. Project Background and Technical Goals

This project was initiated to control a large-scale LED video wall covering an area of 20m². Displaying video on such a large screen requires the organic control of thousands of LED panels. Existing industrial control equipment is characterized by high costs and closed architectures. This project combines off-the-shelf hardware and open-source software to achieve real-time transmission and synchronization of high-definition video at 60 frames per second (60 FPS). The primary goal is to minimize latency from data input to screen output, ensuring a display environment without frame drops or visual misalignment. Specifically, the project utilizes the W5500 to ensure network communication reliability and maximize real-time synchronization performance.

2. Key Technical Elements and Selection Reasons (Methodology)

Components were selected based on performance and cost-efficiency for the system configuration.

Central Controller (Intel N100): Selected for its ability to process and segment high-definition video data in real-time while operating at low power.

Ethernet Controller (WIZnet W5500): This chip features a hardware TCP/IP stack, allowing it to receive large volumes of video packets without consuming MCU software processing resources. It was adopted as a core component due to its low latency and high communication stability.

Node Controller (Raspberry Pi Pico 2 / Pico W): Utilizes the dual-core architecture and Programmable I/O (PIO) of the RP2350 chipset to send signals to LED panels with precise timing. Its low cost makes it suitable for deployment across hundreds of units.

LED Panel (64x64 HUB75): Utilizes 800 standard LED modules. The HUB75 interface supports high-speed data transfer and offers cost benefits for bulk procurement.

3. In-depth Analysis of Hardware Operating Principles (Hardware Mechanics)

The system operates on a distributed architecture where a single central controller manages hundreds of Raspberry Pi Pico controllers.

Video Data Segmentation: The central Intel N100 computer divides the total video frame into 800 individual segments.

Data Distribution: Segmented video data is transmitted over the network to the W5500 chip of each section, which receives the data and forwards it to the Pico controller.

Physical Connection: Each Pico is connected to an LED panel via a HUB75 cable.

Power Distribution: Driving tens of thousands of LEDs consumes significant power. Multiple Power Supply Units (PSUs) are arranged in parallel to maintain stable voltage across each panel section without voltage drops.

4. Communication Interface: Necessity of 10GbE and W5500 Hardware Stack

Data transmission speed and processing methods are critical for real-time 60 FPS video output.

10GbE Backbone: The total required bandwidth is approximately 1.5 Gbps. A 10-Gigabit Ethernet environment was established to prevent bottlenecks that would occur on a standard 1 Gbps network.

W5500 Hardware TCP/IP Offloading: Unlike software-based network processing (such as LWIP), the W5500 handles communication protocols via hardware logic. This allows the MCU to dedicate its resources entirely to LED control rather than network management.

UDP Multicast and IGMP Snooping: Data is transmitted to multiple controllers simultaneously to increase efficiency, while the network switch delivers packets only to the necessary nodes to prevent traffic waste.

5. Software Implementation and Optimization (Software & Coding)

Several optimization techniques were applied at the software level to maximize system performance.

W5500 SPI Optimization: Latency in data transfer was minimized through high-speed SPI communication between the MCU and the W5500.

Zero-Copy: This eliminates unnecessary data copying within memory. By processing received data immediately, CPU load is reduced and speed is increased.

Heapless & No GC: The system avoids Garbage Collection (GC) to prevent execution pauses for memory cleanup, ensuring deterministic operation.

Dual-Core Parallel Processing:

Core 0: Rapidly receives and organizes Ethernet data packets from the W5500.

Core 1: Converts the organized data into signals compatible with the LED panels for output.

Stride Logic: An efficient algorithm extracts the specific pixel data required for a panel from the total data stream at precise intervals.

6. Project Result and Conclusion

This project demonstrates that a large-scale LED system can be reliably controlled using the W5500 hardware communication chip and general-purpose components.

Technical Achievement: Achieved 60 FPS output, providing smooth motion identical to actual video. Hardware-based network processing is the key factor in system stability.

Scalability: The architecture allows expansion beyond 800 panels by simply adding W5500-based control nodes and network equipment.

Conclusion: The project resulted in an economical and efficient open-source solution for large-scale display control, capable of replacing expensive proprietary equipment.

1. 프로젝트 배경 및 기술적 목표

이 프로젝트는 20m²(약 6평) 크기의 거대한 LED 비디오 월을 제어하기 위해 시작되었습니다. 대형 화면에 영상을 출력하려면 수천 개의 LED 패널을 유기적으로 제어해야 합니다. 기존의 산업용 제어 장비는 가격이 매우 높고 폐쇄적인 구조를 가지고 있습니다. 이 프로젝트는 누구나 구할 수 있는 범용 하드웨어와 오픈소스 소프트웨어를 조합하여, 초당 60프레임(60 FPS)의 고화질 영상을 실시간으로 전송하고 동기화하는 것을 목표로 합니다. 데이터 입력부터 화면 출력까지 발생하는 지연 시간(Latency)을 최소화하여 영상의 끊김이나 어긋남이 없는 대형 디스플레이 환경을 구축하고자 합니다. 특히 W5500을 활용하여 네트워크 통신의 신뢰성을 확보하고 실시간 동기화 성능을 극대화하는 데 초점을 맞추고 있습니다.

2. 핵심 기술 요소 및 선정 이유 (Methodology)

시스템 구성을 위해 성능과 비용의 효율성을 고려한 부품들을 선정하였습니다.

중앙 컨트롤러 (Intel N100): 저전력으로 작동하면서 고화질 영상 데이터를 실시간으로 처리하고 분할할 수 있는 성능을 갖추고 있어 선정되었습니다.

이더넷 컨트롤러 (WIZnet W5500): 하드웨어 TCP/IP 스택을 내장하여 MCU의 소프트웨어 연산 부담 없이 대량의 영상 데이터를 수신할 수 있습니다. 지연 시간이 짧고 통신 안정성이 매우 높아 핵심 부품으로 채택되었습니다.

말단 제어기 (Raspberry Pi Pico 2 / Pico W): RP2350 칩셋의 듀얼 코어 구조와 프로그래밍 가능한 입출력(PIO) 기능을 활용하여 LED 패널에 정확한 타이밍으로 신호를 보냅니다. 가격이 저렴하여 수백 개를 투입하기에 적합합니다.

LED 패널 (64x64 HUB75): 표준 규격의 LED 모듈 800개를 사용합니다. HUB75 인터페이스는 빠른 데이터 전송이 가능하며 대량 구매 시 비용 절감 효과가 큽니다.

3. 하드웨어 작동 원리에 대한 심층 분석 (Hardware Mechanics)

시스템은 하나의 중앙 컨트롤러가 수백 개의 Raspberry Pi Pico 제어기를 관리하는 '분산형 구조'로 작동합니다.

영상 데이터 분할: 중앙의 Intel N100 컴퓨터가 전체 영상을 800개의 구역으로 잘게 나눕니다.

데이터 배분: 분할된 영상 조각들은 네트워크를 통해 각 구역의 W5500 칩으로 전달되며, W5500은 이를 수신하여 Pico 제어기로 전송합니다.

물리적 연결: 각 Pico는 HUB75 케이블을 통해 LED 패널과 연결됩니다.

전원 공급 구조: 수만 개의 LED 소자가 동시에 빛을 내면 막대한 전력이 소모됩니다. 이를 위해 다수의 전원 공급 장치(PSU)를 병렬로 배치하여 각 패널 구역에 전압 강하 없이 안정적인 전력을 공급하도록 설계되었습니다.

4. 통신 인터페이스: 10GbE와 W5500 하드웨어 스택의 필요성

고화질 영상을 실시간으로 출력하기 위해서는 데이터 전송 속도와 처리 방식이 매우 중요합니다.

10GbE 백본망: 전체 시스템이 요구하는 총 데이터 대역폭은 약 1.5Gbps에 달합니다. 일반적인 1Gbps망으로는 부족하기 때문에 10기가비트 이더넷 환경을 구축하여 데이터 병목 현상을 방지하였습니다.

W5500 Hardware TCP/IP Offloading: 소프트웨어 방식의 네트워크 처리(LWIP 등)와 달리, W5500은 통신 프로토콜 처리를 하드웨어 로직으로 수행합니다. 이로 인해 MCU는 네트워크 관리에 자원을 소모하지 않고 오직 LED 제어에만 전념할 수 있습니다.

UDP 멀티캐스트 및 IGMP Snooping: 데이터를 여러 제어기에 동시에 전송하여 효율을 높이고, 네트워크 스위치에서 필요한 곳에만 패킷을 전달하여 트래픽 낭비를 막습니다.

5. 소프트웨어 구현 및 최적화 (Software & Coding)

시스템의 성능을 극한으로 끌어올리기 위해 소프트웨어 차원에서 여러 최적화 기법을 적용하였습니다.

W5500 SPI 최적화: MCU와 W5500 사이의 고속 SPI 통신을 통해 데이터 전송 지연을 최소화하였습니다.

Zero-Copy: 데이터가 메모리 내에서 다른 곳으로 복사되는 불필요한 과정을 제거했습니다. 수신된 데이터를 즉시 처리하여 CPU의 부담을 줄이고 속도를 높였습니다.

Heapless & No GC: 가비지 컬렉션(GC) 기능을 사용하지 않도록 설계하여, 프로그램이 실행 도중 메모리 정리 작업을 위해 멈추는 현상을 원천 차단했습니다.

듀얼 코어 병렬 처리:

Core 0: W5500으로부터 들어오는 이더넷 데이터 패킷을 빠르게 수신하고 순서를 정리합니다.

Core 1: 정리된 데이터를 LED 패널이 인식할 수 있는 신호로 변환하여 출력합니다.

Stride Logic: 전체 데이터 덩어리에서 해당 패널에 필요한 픽셀 데이터만 정확한 간격으로 추출하는 효율적인 알고리즘을 사용합니다.

6. 프로젝트 결과 및 결론

이 프로젝트는 W5500 하드웨어 통신 칩과 범용 부품만으로도 대규모 LED 시스템을 안정적으로 제어할 수 있음을 증명했습니다.

기술적 성과: 초당 60프레임의 화면 출력을 달성하여 실제 영상과 차이가 없는 매끄러운 움직임을 구현하였습니다. 하드웨어 기반의 네트워크 처리가 시스템 안정성에 기여한 핵심 요소입니다.

확장성: 800개 이상의 패널로 시스템을 확장하더라도 W5500 기반의 제어 노드와 네트워크 장비만 추가하면 되는 구조를 갖추고 있습니다.

결론: 고가의 전용 장비를 대체할 수 있는 경제적이고 효율적인 오픈소스 대형 디스플레이 제어 솔루션을 완성하였습니다.

출처 및 관련 링크: