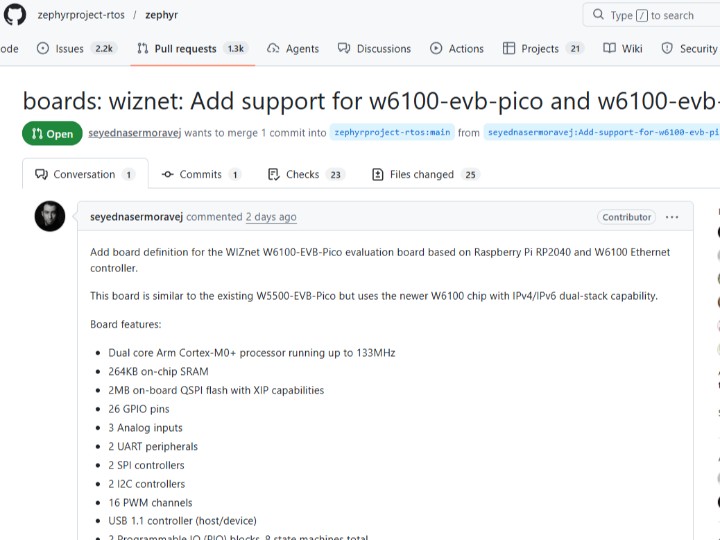

Zephyr PR #104394: Architecture Analysis of W6100-EVB-Pico & Pico2

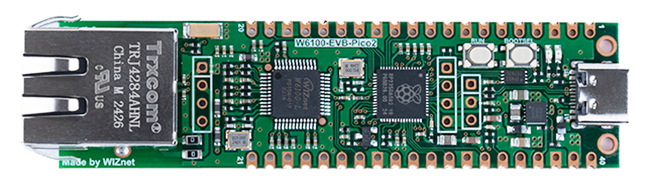

Zephyr PR #104394 brings W6100-EVB-Pico2 support! It pairs RP2350 with W6100 (IPv6) and enables high-speed 70MHz SPI.

Software Apps and online services

This PR goes beyond simply adding board names; it serves as a significant technical reference demonstrating how the Zephyr Hardware Abstraction Layer (HAL) defines and controls the RP2350 (Pico 2) and W6100.

We have analyzed the key modified files to summarize the core technical details regarding hardware definitions and system configurations.

1. Device Tree (.dts) Analysis: Hardware Definition of W6100

The core of this update lies in the boards/wiznet/w6100_evb_pico2/w6100_evb_pico2.dtsi file. This defines how the Zephyr kernel recognizes and communicates with the W6100 chip.

Ethernet Node Configuration

The ethernet node is bound under the RP2350's spi0 bus.

/* Excerpt from w6100_evb_pico2.dtsi */

&spi0 {

clock-frequency = <DT_FREQ_M(8)>; /* Default SPI clock 8MHz */

status = "okay";

cs-gpios = <&gpio0 17 GPIO_ACTIVE_LOW>; /* Chip Select: GP17 */

ethernet: w6100@0 {

compatible = "wiznet,w6100";

reg = <0x0>;

/* Note: SPI max speed set to 70MHz to maximize performance */

spi-max-frequency = <70000000>;

/* Interrupt and Reset pin definitions */

int-gpios = <&gpio0 21 GPIO_ACTIVE_LOW>;

reset-gpios = <&gpio0 20 GPIO_ACTIVE_LOW>;

/* Initial MAC address (Needs to be changed for production) */

local-mac-address = [00 00 00 01 02 03];

status = "okay";

};

};- Performance Point: The

spi-max-frequencyis set to<70000000>(70MHz). This setting is close to the W6100's maximum specification, indicating an intention to secure high throughput within the Zephyr network stack.

2. Pin Multiplexing (pinctrl) Analysis

While the RP2350 allows for flexible pin functions, this board requires fixed pin assignments to match the hardware circuitry. This is handled in w6100_evb_pico2-pinctrl.dtsi.

SPI0 Pin Mapping

spi0_default: spi0_default {

group1 {

pinmux = <SPI0_CSN_P17>, <SPI0_SCK_P18>, <SPI0_TX_P19>;

};

group2 {

pinmux = <SPI0_RX_P16>;

input-enable; /* Input enable is mandatory for RX pins */

};

};RP2350 Pin Allocation:

- SPI0 RX (MISO): GP16

- SPI0 CSn: GP17

- SPI0 SCK: GP18

- SPI0 TX (MOSI): GP19

- It maintains the same pinout as previous W5100S/W5500 EVB boards based on the Raspberry Pi Pico , ensuring hardware compatibility.

3. Kconfig and System Configuration Analysis

The Kconfig.defconfig and .yaml files reveal how the Zephyr build system handles this board.

Default Configuration (Kconfig.defconfig)

if BOARD_W6100_EVB_PICO2

config NET_L2_ETHERNET

default y

config USB_SELF_POWERED

default n

endifNET_L2_ETHERNET default y: When building for this target, Zephyr's L2 Ethernet layer is automatically activated. Developers do not need to manually add Ethernet settings toprj.confto use network functions immediately.

Architecture Definition (.yaml)

identifier: w6100_evb_pico2/rp2350a/m33

type: mcu

arch: arm

toolchain:

- zephyr

- gnuarmemb

ram: 520 # Reflects the expanded 520KB SRAM of RP2350

flash: 2048- Target Core: It is explicitly specified as

rp2350a/m33, indicating it builds for the RP2350's Arm Cortex-M33 core. - Memory: The

ram: 520setting ensures the build system recognizes the expanded memory (520KB) compared to the RP2040 (264KB). This provides a significant advantage when running heavy security libraries (like mbedTLS) alongside the W6100 driver.

Community Interest & Next Steps

Although this PR (#104394) was opened very recently, it has already attracted significant attention from the Zephyr community. Notably, 6 reviews have already been posted by key maintainers, signaling strong interest in the official support for the RP2350 and W6100 combination.

This rapid feedback loop suggests that this board support is highly anticipated. We encourage the WIZnet Maker community to check out the PR, test the code if possible, and show your support to help expedite the merge process!

💡 FAQ

Q1. How does the RP2350's increased specification benefit W6100 network applications?

- A: The RP2350's 520KB of SRAM is a significant advantage. Running network applications on Zephyr often requires substantial memory for packet buffers (

net_pkt) and security libraries like mbedTLS. The increased RAM allows for more stable SSL/TLS connections and larger buffer sizes without running out of heap memory.

Q2. Is the hardware pinout compatible with previous WIZnet Pico boards?

- A: Yes. According to the

pinctrldefinitions in the PR, the SPI bus (GP16-GP19) and control pins (CS: GP17, RST: GP20, INT: GP21) remain consistent with the previous W5100S/W5500-EVB-Pico boards. This ensures that existing expansion boards or shields designed for the Pico form factor can be reused.

Q3. Can I use this board in Zephyr right now?

- A: Since PR #104394 is still under review, it is not yet available in the main Zephyr branch. To use it immediately, you must fetch the PR branch manually or wait for it to be merged into the mainline. The active review status suggests it may be integrated soon.

[View PR #104394 on GitHub] https://github.com/zephyrproject-rtos/zephyr/pull/104394