How to Configure a Static-IP Ethernet Stack with W5500 on ESP32?

This article focuses on using an ESP32 with a W5500 Ethernet module under ESP-IDF, with emphasis on static IP setup,

How to Configure a Static-IP Ethernet Stack with W5500 on ESP32?

Summary

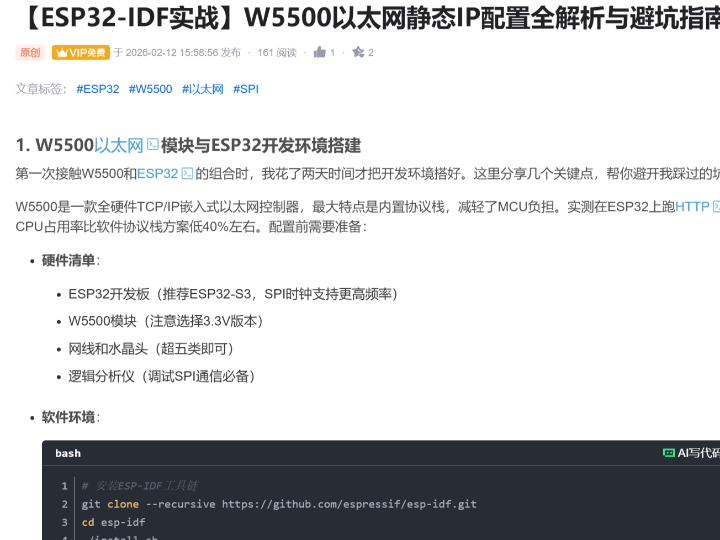

This article focuses on using an ESP32 with a W5500 Ethernet module under ESP-IDF, with emphasis on static IP setup, SPI-based wired integration, and common configuration mistakes that break bring-up. In this design, the ESP32 runs the application and ESP-IDF Ethernet framework, while the W5500 provides the external wired Ethernet path and hardware TCP/IP offload over SPI.

What the Project Does

The source is a practical ESP32 + W5500 bring-up guide rather than a full public project repository. It covers environment setup with ESP-IDF, recommended ESP32-to-W5500 SPI pin mapping, and the sequence required to get static IP working reliably on a W5500-backed Ethernet interface. The article frames the main pain point as not just “how to attach W5500,” but how to avoid the common missteps that make Ethernet appear broken when the real problem is setup order.

From a network-stack perspective, this is an ESP-IDF Ethernet integration built around the W5500 as an SPI-attached controller rather than a raw register-only demo. The guide states that ESP-IDF’s esp_eth driver already supports W5500, then moves into SPI bus setup and static IP behavior. That makes it useful for makers because it shows the boundary between board-level SPI transport, ESP-IDF driver integration, and network identity management.

Architecturally, the system is simple and appropriate for maker wired Ethernet nodes: ESP32 provides compute, application logic, and driver orchestration; W5500 provides the wired Ethernet controller with its embedded TCP/IP function; and the application sits above ESP-IDF’s Ethernet and IP configuration layers. The article specifically positions this combination as lower CPU overhead than a software-stack approach, but that performance figure is presented as the author’s claim rather than a reproducible benchmark.

Where WIZnet Fits

The exact WIZnet part here is the W5500. Its role is the external Ethernet controller connected over SPI to the ESP32. WIZnet’s official documentation describes the W5500 as a hardwired TCP/IP controller with integrated 10/100 Ethernet MAC and PHY, 32 KB internal memory, and support for eight independent sockets via an SPI host interface. Those characteristics explain why it is a practical fit for ESP32 maker projects that want wired Ethernet without pulling a full software TCP/IP implementation into the MCU side.

In this article’s architecture, W5500 is the network endpoint under ESP-IDF’s Ethernet layer. The MCU still owns SPI bus initialization, pin mapping, interrupt handling, application logic, and IP configuration policy, but the W5500 owns the Ethernet-side transport machinery. That separation is what makes the project approachable for makers: the firmware can stay close to driver setup and IP configuration instead of becoming a full low-level Ethernet implementation.

Implementation Notes

This project does use WIZnet products, and the article shows real inline code fragments, but it does not provide a public repository with file paths or line-addressable source files. I therefore cannot verify a repo-backed codebase, and I am limiting code references to what is visible in the article itself.

One visible implementation block is the SPI bus setup in ESP-IDF:

spi_bus_config_t buscfg = {.miso_io_num = GPIO_NUM_19,.mosi_io_num = GPIO_NUM_23,.sclk_io_num = GPIO_NUM_18,.quadwp_io_num = -1,.quadhd_io_num = -1};

Why it matters: this is the physical transport boundary between ESP32 and W5500. The article’s recommended mapping is GPIO23 to MOSI, GPIO19 to MISO, GPIO18 to SCLK, GPIO5 to chip select, and GPIO26 to INT, which is exactly the kind of board-level detail that determines whether the Ethernet stack ever comes up. The article also warns that the W5500 reset pin should have a 10 kΩ pull-up because missing reset conditioning caused repeated initialization failures in the author’s own bring-up.

The article also makes a concrete architecture claim about the software stack: ESP-IDF’s official esp_eth driver already includes W5500 support, so the main firmware task is not writing a full Ethernet stack but configuring the driver and applying static IP correctly. Why it matters: that is the core engineering value of this project. The W5500 is used as a supported Ethernet endpoint inside ESP-IDF rather than as an isolated peripheral with ad hoc networking code.

Because the paywalled section obscures part of the article’s code, I cannot quote a longer verified static-IP snippet from the source. But the article title, visible setup section, and surrounding explanation make the focus clear: this is a static-IP configuration guide for ESP32 + W5500 under ESP-IDF, with the main lesson being correct initialization order and wiring stability rather than novel protocol logic.

Practical Tips / Pitfalls

Use the exact SPI wiring consistently during first bring-up: GPIO23 to MOSI, GPIO19 to MISO, GPIO18 to SCLK, GPIO5 to CS, and GPIO26 to INT. Miswiring here will look like a software problem later.

Add a proper pull-up on the W5500 reset line. The article explicitly says missing reset conditioning caused initialization failures until it was corrected.

Treat a logic analyzer as a first-line debug tool, not an optional accessory. The article lists it as essential for SPI debugging, which is sensible for W5500 bring-up on ESP32.

Do not over-trust performance claims from blog posts. The article says CPU usage was about 40% lower than a software-stack approach when running an HTTP server on ESP32, but it does not publish enough methodology to verify that independently.

Keep the architecture simple at first: SPI bus, reset, driver install, then static IP. Avoid adding application protocols until wired connectivity is stable. This is an inference from the article’s sequencing and ESP-IDF integration model.

FAQ

Why use W5500 with ESP32 for this project?

Because it gives ESP32 a wired Ethernet path through a hardware TCP/IP controller instead of forcing the firmware to build everything around a pure software solution. W5500’s integrated MAC/PHY, internal memory, and socket-based hardware model make it a practical external Ethernet controller for small MCU systems.

How does it connect to the platform?

The article recommends an SPI connection using GPIO23 for MOSI, GPIO19 for MISO, GPIO18 for SCLK, GPIO5 for chip select, and GPIO26 for interrupt. It also highlights reset-line conditioning as important for reliable power-up.

What role does it play in this specific project?

It is the wired Ethernet controller under ESP-IDF’s Ethernet framework. ESP32 handles application logic and driver orchestration, while W5500 provides the actual Ethernet-side transport and offloaded stack behavior.

Can beginners follow this project?

Yes, if they already know basic ESP-IDF workflow and SPI wiring. The article is better suited to makers learning practical Ethernet bring-up than to complete beginners, because the useful part of the exercise is understanding why pin mapping, reset behavior, and configuration order matter.

How does this compare with Wi-Fi on ESP32?

Wi-Fi is easier for untethered deployment, but this project is aimed at cases where wired stability and deterministic local networking matter more. W5500 also reduces some firmware-side burden by using a hardware TCP/IP model. The article implies efficiency benefits, but does not provide enough controlled data for a strict performance comparison.

Source

Original article: CSDN post, “〖ESP32-IDF实战〗W5500以太网静态IP配置全解析与避坑指南,” published February 12, 2026. The visible content includes hardware setup, SPI pin mapping, reset advice, and ESP-IDF SPI bus configuration for W5500. Product facts were checked against WIZnet’s official W5500 overview and datasheet.

Tags

W5500, WIZnet, ESP32, ESP-IDF, Ethernet, SPI, Static IP, Wired Networking, Network Stack, Maker, Embedded Ethernet, TCP/IP Offload

ESP32에서 W5500으로 고정 IP 이더넷 스택을 어떻게 설정할 수 있을까?

Summary

이 글은 ESP-IDF 환경에서 ESP32와 W5500 이더넷 모듈을 사용하는 방법을 다루며, 특히 고정 IP 설정, SPI 기반 유선 통합, 그리고 초기 구동을 망치는 대표적인 설정 실수에 초점을 맞춘다. 이 구조에서 ESP32는 애플리케이션과 ESP-IDF 이더넷 프레임워크를 실행하고, W5500은 SPI를 통해 연결되는 외부 유선 이더넷 경로이자 하드웨어 TCP/IP 오프로딩 장치 역할을 한다.

What the Project Does

이 소스는 완전한 공개 프로젝트 저장소라기보다 ESP32 + W5500 초기 구동 가이드에 가깝다. 내용은 ESP-IDF 개발 환경 준비, ESP32와 W5500 사이의 권장 SPI 핀 연결, 그리고 W5500 기반 이더넷 인터페이스에서 고정 IP가 제대로 동작하도록 만드는 설정 순서를 중심으로 구성된다. 글은 핵심 문제를 단순히 “W5500을 어떻게 연결하느냐”로 보지 않고, 실제로는 설정 순서가 잘못되어 이더넷이 고장 난 것처럼 보이는 상황을 어떻게 피하느냐에 둔다.

네트워크 스택 관점에서 보면, 이것은 W5500 레지스터를 직접 만지는 단순 데모가 아니다. ESP-IDF의 esp_eth 드라이버가 이미 W5500을 지원한다는 점을 바탕으로, SPI 버스 설정과 고정 IP 동작으로 이어지는 흐름을 설명한다. 그래서 메이커 입장에서는 보드 수준 SPI 연결, ESP-IDF 드라이버 통합, 네트워크 식별 정보 관리가 어디에서 나뉘는지를 이해하는 데 도움이 된다.

아키텍처는 단순하고 메이커용 유선 이더넷 노드에 잘 맞는다. ESP32는 연산, 애플리케이션 로직, 드라이버 오케스트레이션을 담당하고, W5500은 내장 TCP/IP 기능을 포함한 유선 이더넷 컨트롤러 역할을 하며, 애플리케이션은 그 위의 ESP-IDF 이더넷 및 IP 설정 계층 위에서 동작한다. 글은 이 조합이 순수 소프트웨어 스택 접근보다 CPU 부담이 낮다고 설명하지만, 그 수치는 작성자 주장이며 재현 가능한 벤치마크로 제시되지는 않는다.

Where WIZnet Fits

여기서 사용된 정확한 WIZnet 부품은 W5500이다. 역할은 ESP32에 SPI로 연결되는 외부 이더넷 컨트롤러다. WIZnet 공식 문서에 따르면 W5500은 하드와이어드 TCP/IP 컨트롤러이며, 통합 10/100 Ethernet MAC 및 PHY, 32 KB 내부 메모리, 8개의 독립 소켓, SPI 호스트 인터페이스를 제공한다. 이런 특성 때문에 ESP32 메이커 프로젝트에서 전체 소프트웨어 TCP/IP 구현을 MCU 쪽으로 끌고 오지 않으면서 유선 이더넷을 붙이기에 적합하다.

이 글의 아키텍처에서 W5500은 ESP-IDF 이더넷 계층 아래의 네트워크 엔드포인트 역할을 한다. MCU는 여전히 SPI 버스 초기화, 핀 매핑, 인터럽트 처리, 애플리케이션 로직, IP 설정 정책을 담당하지만, W5500이 실제 이더넷 측 전송 메커니즘을 맡는다. 이 분리가 메이커 프로젝트를 접근 가능하게 만든다. 펌웨어가 전체 저수준 이더넷 구현으로 가지 않고, 드라이버 설정과 IP 구성 중심으로 유지될 수 있기 때문이다.

Implementation Notes

이 프로젝트는 실제로 WIZnet 제품을 사용하며, 글 안에는 실제 코드 조각도 보인다. 다만 공개 저장소나 파일 경로, 줄 번호를 확인할 수 있는 소스는 제공되지 않는다. 따라서 저장소 기반 검증은 할 수 없고, 아래 설명은 글 안에서 확인 가능한 코드와 설명만 기준으로 한다.

눈에 보이는 구현 블록 중 하나는 ESP-IDF의 SPI 버스 설정이다.

spi_bus_config_t buscfg = {.miso_io_num = GPIO_NUM_19,.mosi_io_num = GPIO_NUM_23,.sclk_io_num = GPIO_NUM_18,.quadwp_io_num = -1,.quadhd_io_num = -1};

이 코드가 중요한 이유는 ESP32와 W5500 사이의 물리적 전송 경계를 보여주기 때문이다. 글은 GPIO23을 MOSI, GPIO19를 MISO, GPIO18을 SCLK, GPIO5를 칩 셀렉트, GPIO26을 INT로 권장한다. 이런 보드 수준 세부사항이 실제로 이더넷 스택이 올라올지 말지를 결정한다. 글은 또 W5500 리셋 핀에 10 kΩ 풀업 저항을 넣어야 한다고 강조하는데, 실제로 리셋 조건이 불안정해서 초기화가 반복 실패했던 경험을 근거로 제시한다.

글은 소프트웨어 스택 측면에서도 분명한 구조를 제시한다. ESP-IDF 공식 esp_eth 드라이버가 이미 W5500을 지원하므로, 개발의 핵심은 전체 이더넷 스택을 새로 쓰는 것이 아니라, 드라이버를 올바르게 설정하고 고정 IP를 정확한 순서로 적용하는 것이다. 이것이 바로 이 프로젝트의 실질적인 공학적 가치다. W5500을 별도의 고립된 주변장치처럼 다루지 않고, ESP-IDF 안에서 지원되는 이더넷 엔드포인트로 통합하는 방식이기 때문이다.

다만 유료 구간 때문에 기사 일부 코드가 가려져 있어, 고정 IP 설정에 대한 더 긴 검증 가능한 코드 조각은 직접 인용할 수 없다. 그래도 제목, 보이는 설정 구간, 주변 설명을 종합하면 초점은 분명하다. 이것은 ESP-IDF 환경의 ESP32 + W5500에 대한 고정 IP 구성 가이드이며, 핵심 교훈은 새로운 프로토콜 로직이 아니라 올바른 초기화 순서와 안정적인 배선이다.

Practical Tips / Pitfalls

첫 구동에서는 SPI 배선을 정확히 맞추는 것이 가장 중요하다. GPIO23은 MOSI, GPIO19는 MISO, GPIO18은 SCLK, GPIO5는 CS, GPIO26은 INT로 유지하는 편이 좋다. 여기서 틀리면 나중에 소프트웨어 문제처럼 보인다.

W5500 리셋 라인에는 적절한 풀업을 넣는 편이 좋다. 글은 리셋 조건이 불안정하면 초기화 실패가 반복된다고 분명히 말한다.

로직 애널라이저는 선택 장비가 아니라 1차 디버깅 도구로 보는 편이 맞다. 글도 SPI 디버깅에 필수라고 권장한다.

블로그의 성능 수치는 그대로 믿기보다 참고 수준으로 보는 편이 좋다. 글은 ESP32에서 HTTP 서버를 돌릴 때 CPU 사용량이 소프트웨어 스택 대비 약 40% 낮았다고 주장하지만, 이를 독립적으로 검증할 수 있을 만큼 충분한 측정 조건은 제시하지 않는다.

처음에는 구조를 단순하게 유지하는 것이 좋다. SPI 버스, 리셋, 드라이버 설치, 고정 IP 설정까지 안정화한 뒤에 애플리케이션 프로토콜을 올리는 편이 낫다.

FAQ

왜 이 프로젝트에서 ESP32와 함께 W5500을 사용하는가?

ESP32에 유선 이더넷 경로를 하드웨어 TCP/IP 컨트롤러 기반으로 추가할 수 있기 때문이다. W5500은 통합 MAC/PHY, 내부 메모리, 소켓 중심 하드웨어 모델을 제공하므로, 소형 MCU 시스템에서 실용적인 외부 이더넷 컨트롤러 역할을 한다.

플랫폼과는 어떻게 연결되는가?

글은 SPI 연결을 권장한다. GPIO23은 MOSI, GPIO19는 MISO, GPIO18은 SCLK, GPIO5는 칩 셀렉트, GPIO26은 인터럽트에 사용한다. 또한 안정적인 전원 인가를 위해 리셋 라인 처리도 중요하다고 강조한다.

이 프로젝트에서 W5500의 역할은 무엇인가?

ESP-IDF 이더넷 프레임워크 아래에서 동작하는 유선 이더넷 컨트롤러다. ESP32는 애플리케이션 로직과 드라이버 오케스트레이션을 담당하고, W5500은 실제 이더넷 측 전송과 오프로딩된 스택 동작을 담당한다.

초보자도 이 프로젝트를 따라갈 수 있는가?

가능하다. 다만 기본적인 ESP-IDF 개발 흐름과 SPI 배선은 알고 있는 편이 좋다. 이 글은 완전 초보보다는, 실제 이더넷 초기 구동에서 왜 핀 매핑, 리셋 동작, 설정 순서가 중요한지 배우려는 메이커에게 더 적합하다.

ESP32의 Wi-Fi와 비교하면 어떤 차이가 있는가?

Wi-Fi는 무선 배포에 유리하지만, 이 프로젝트는 유선의 안정성과 예측 가능한 로컬 네트워킹이 더 중요한 경우를 다룬다. W5500은 하드웨어 TCP/IP 모델을 사용하므로 MCU 펌웨어 부담을 줄여줄 수 있다. 다만 글에 나온 효율 비교는 엄격한 성능 비교 자료로 보기에는 근거가 충분하지 않다.

Source

원문 출처: CSDN 글 “〖ESP32-IDF实战〗W5500以太网静态IP配置全解析与避坑指南”, 2026년 2월 12일 게시.

보이는 내용에는 하드웨어 설정, SPI 핀 매핑, 리셋 관련 주의사항, ESP-IDF SPI 버스 설정이 포함되어 있다. 제품 관련 사실은 WIZnet 공식 W5500 개요 및 데이터시트를 기준으로 확인했다.

Tags

W5500, WIZnet, ESP32, ESP-IDF, Ethernet, SPI, Static IP, Wired Networking, Network Stack, Maker, Embedded Ethernet, TCP/IP Offload