How Does STM32 Communicate with W5500 at the Register Level?

This article explains how an STM32 microcontroller communicates with the WIZnet W5500 Ethernet controller through SPI at the register level.

How Does STM32 Communicate with W5500 at the Register Level?

SPI Transaction Rules and Network Setup Explained for Reliable Ethernet Bring-Up

(STM32와 W5500은 레지스터 수준에서 어떻게 통신하는가?)

Summary (40–60 words)

This article explains how an STM32 microcontroller communicates with the WIZnet W5500 Ethernet controller through SPI at the register level. By analyzing SPI frame structure, chip-select timing, and network configuration registers, it shows how correct low-level handling enables reliable Ethernet bring-up before any TCP or UDP sockets are used.

1. Why SPI-Level Understanding Matters More Than Applications

Many Ethernet issues on embedded systems appear before any socket is opened:

Link LED is on, but ping fails

Network works once, then stops after reset

Registers read back incorrect values

In STM32 + W5500 systems, these problems almost always originate from SPI communication discipline and register sequencing, not TCP or application logic.

If SPI and registers are wrong, higher-layer protocols never had a chance.

2. STM32 ↔ W5500 Hardware Communication Model

Architectural Separation

STM32:

Executes firmware logic

Parses data

Controls peripherals

W5500:

Implements Ethernet MAC + PHY

Implements full hardware TCP/IP

Exposes configuration and data through registers

All interaction happens through SPI register access.

3. W5500 SPI Frame Structure (Critical Detail)

Every SPI transaction to W5500 follows a strict, multi-byte frame:

16-bit address

Register offset within a block

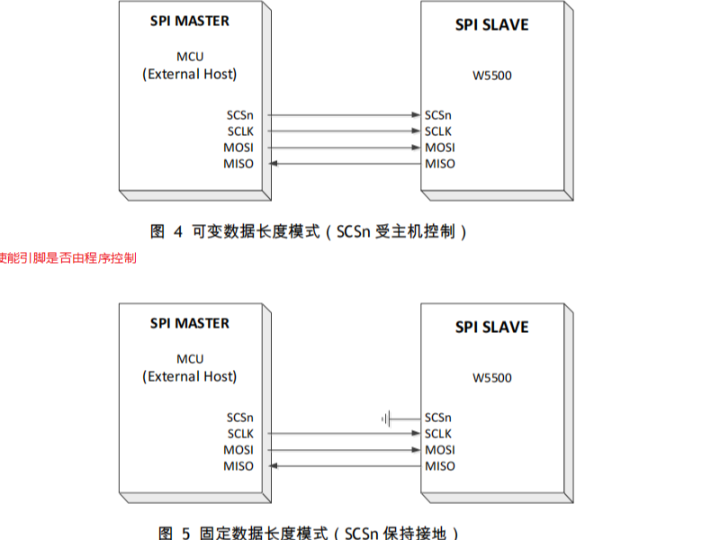

8-bit control byte

Read / Write bit

Block select (common, socket, TX, RX)

Data mode (variable or fixed length)

Data bytes

This design allows W5500 to expose its entire internal memory map over SPI.

4. Chip Select (CS) Timing Rules

The Golden Rule

CS must remain LOW for the entire SPI frame — from address to last data byte.

Violations cause:

Partial register writes

Block selection errors

Corrupted network configuration

On STM32, this means:

No CS toggling inside HAL SPI calls

No interrupt-driven SPI access without protection

Extra care when using DMA

Many “mysterious” Ethernet bugs originate here.

5. Reset Sequence and SPI Readiness

Before any SPI access:

Assert W5500 RESET low

Hold for the minimum datasheet time

Release RESET

Wait for internal stabilization

Why this matters:

Internal registers reset to known values

PHY and socket logic initialize correctly

Writing registers too early leads to undefined behavior.

6. Register-Level Network Setup Flow

Network bring-up requires configuring common registers in the W5500.

Mandatory Configuration Order

MAC address

IPv4 address

Subnet mask

Gateway address

These registers define the device’s network identity.

Important distinction:

A physical Ethernet link does not imply IP-level connectivity.

Until these registers are written correctly, the device is invisible on the network.

7. SPI Access Patterns for Register Writes

Best practices for STM32 firmware:

Write registers using variable-length SPI mode

Group related register writes to minimize CS toggling

Read back registers to verify correctness

Reading back values is not optional during bring-up — it is the fastest way to confirm SPI integrity.

8. Verifying Network Configuration at Register Level

After writing network registers:

Read them back over SPI

Compare with expected values

Confirm no byte-order or alignment issues

If values mismatch:

SPI framing is wrong

CS timing is broken

Control byte is misconfigured

Debug here before testing ping or sockets.

9. Common SPI and Register-Level Failure Modes

❌ Link LED on, but cannot ping

Cause:

IP or gateway registers not written

Subnet mismatch

❌ Registers read back incorrectly

Cause:

CS deasserted too early

Wrong SPI mode (CPOL/CPHA)

❌ Network works only after power cycle

Cause:

Reset timing too short

Registers written before W5500 ready

These are deterministic, reproducible errors.

10. Why W5500’s Register Model Is Industrial-Friendly

W5500 uses:

Fixed register addresses

No dynamic memory

Explicit state exposure

This means:

Behavior is predictable

Debugging is straightforward

Long-term stability is achievable

For industrial and field devices, this transparency is a major advantage.

11. Transition from Network Setup to Socket Usage

Only after:

SPI verified

Registers verified

Network reachable

Should firmware proceed to:

TX/RX buffer allocation

Socket initialization

TCP or UDP communication

Skipping these steps guarantees instability.

12. Key Takeaway

In STM32 + W5500 systems, reliable Ethernet starts with SPI discipline and register correctness — not with TCP or application code.

When SPI framing, CS timing, and register sequencing are correct:

Network bring-up is deterministic

Debug time is minimal

Higher-level protocols “just work”

FAQ (Engineer-Focused)

Q1. Does W5500 tolerate SPI timing mistakes?

No. SPI framing must be exact.

Q2. Is HAL SPI safe to use?

Yes, if CS is managed correctly.

Q3. Should registers always be read back?

Yes, especially during bring-up.

Q4. Is this STM32-specific?

No. These rules apply to all MCUs.

Q5. Can this run without an RTOS?

Yes. SPI and register logic are RTOS-independent.

Source

CSDN article: weixin_44742767 (131244488)

WIZnet W5500 Datasheet

Tags

W5500, WIZnet, STM32, SPI Communication, Register-Level Ethernet, Network Bring-Up, Embedded Ethernet

🇰🇷 한국어 번역 (1:1 Full Translation)

STM32와 W5500은 레지스터 수준에서 어떻게 통신하는가?

SPI 통신 규칙과 네트워크 초기화 절차로 이해하는 이더넷 브링업

요약

본 문서는 STM32 마이크로컨트롤러가 WIZnet W5500 이더넷 컨트롤러와 SPI를 통해 레지스터 수준에서 통신하는 방식을 설명한다. SPI 프레임 구조, CS 타이밍, 네트워크 설정 레지스터를 분석함으로써, TCP나 UDP 이전 단계에서 안정적인 이더넷 브링업이 어떻게 이루어지는지를 보여준다.

1. 애플리케이션 이전 단계의 중요성

대부분의 이더넷 문제는

소켓 이전 단계에서 발생한다.

2. SPI 프레임 구조

주소 + 제어 바이트 + 데이터

3. CS 타이밍 규칙

CS는

프레임 전체 동안 유지되어야 한다.

4. 네트워크 레지스터 설정

MAC, IP, 서브넷, 게이트웨이

5. 흔한 오류

CS 조기 해제

잘못된 SPI 모드

리셋 타이밍 부족

6. 핵심 메시지

W5500 이더넷의 신뢰성은 SPI 규율에서 시작된다.

태그

W5500, STM32, SPI 통신, 레지스터 수준 이더넷, 네트워크 브링업