Foenix Labs A2560Me Brings MC68LC060 CPU, FPGA Graphics, and PCIe Expansion

The A2560Me pairs a Motorola MC68LC060 with WIZnet's W6100 and WizFi360, offloading IPv4/IPv6 TCP/IP to hardware on a 66 MHz legacy CPU.

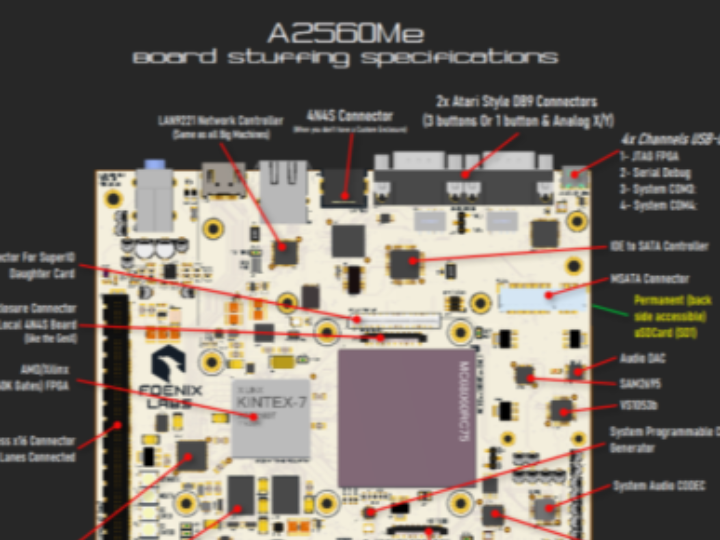

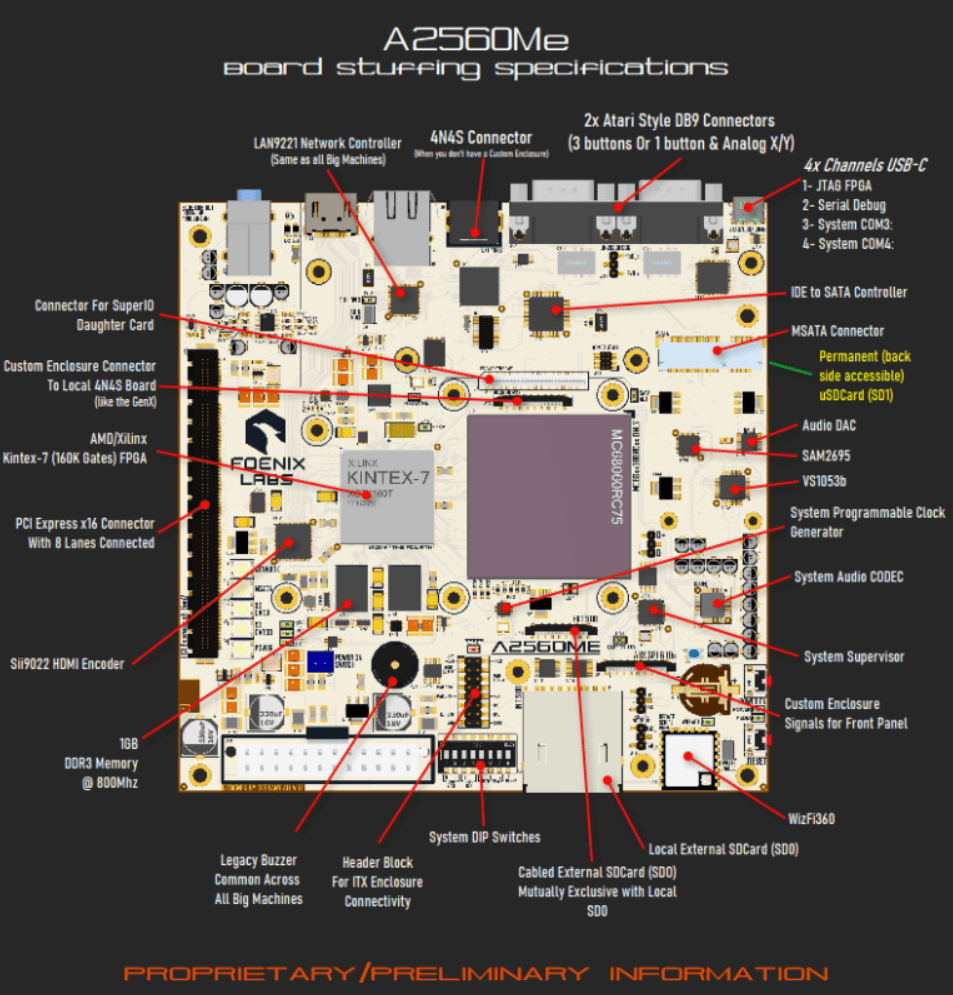

Recently, the hardware community — including technical media like LinuxGizmos — has been paying close attention to 'Modern-Retro' computing projects. These projects go beyond simple software emulation by combining actual legacy silicon (CPUs) with modern I/O. A prime example is the A2560Me motherboard by Foenix Labs.

Built around the Motorola MC68LC060 processor and integrated with WIZnet's W6100 and WizFi360, the board implements a dual-network environment on top of a classic 68k architecture. This article breaks down how that legacy platform connects to modern networks.

1. Project Overview

The A2560Me is a Mini-ITX motherboard combining a Motorola 68k series (32-bit) processor with modern interfaces including PCIe and 1 GB DDR3 memory. Rather than emulation, it represents physical hardware-level integration of legacy and modern components. Primary use cases include:

- Retro Homebrew Development — Open-source communities running legacy/lightweight OSes (EmuTOS, OS-9, etc.) on modern form-factor hardware to develop new software.

- Hardware Architecture Research — Validating data exchange architectures between classic parallel bus systems and modern high-speed interfaces (PCIe, USB).

- Industrial Legacy Equipment Modernization (Retrofitting) — A testbed for connecting older MPU-based industrial equipment to modern smart factory networks (IPv6, Wi-Fi) while preserving the existing control framework.

2. The Challenge: 68k Processor vs. Modern Network Stacks

The most critical bottleneck when designing retro platforms like this is network stack processing.

- Computing overhead — A legacy CPU running at 66 MHz attempting to process complex modern traffic — especially IPv6 packets — entirely in software can saturate the entire system.

- Driver gap — Early-stage lightweight OSes like EmuTOS and FUZIX lack the drivers required to run modern network chipsets.

Solution Foenix Labs addressed this by simultaneously deploying WIZnet's W6100 and WizFi360, offloading all network protocol processing to dedicated hardware.

3. Core Architecture: Dual Interface & Hybrid Network

Using WIZnet solutions, the A2560Me implements a dual-interface design at the physical level and a hybrid network topology at the logical level. Wired and wireless modules are combined heterogeneously, each serving a distinct purpose.

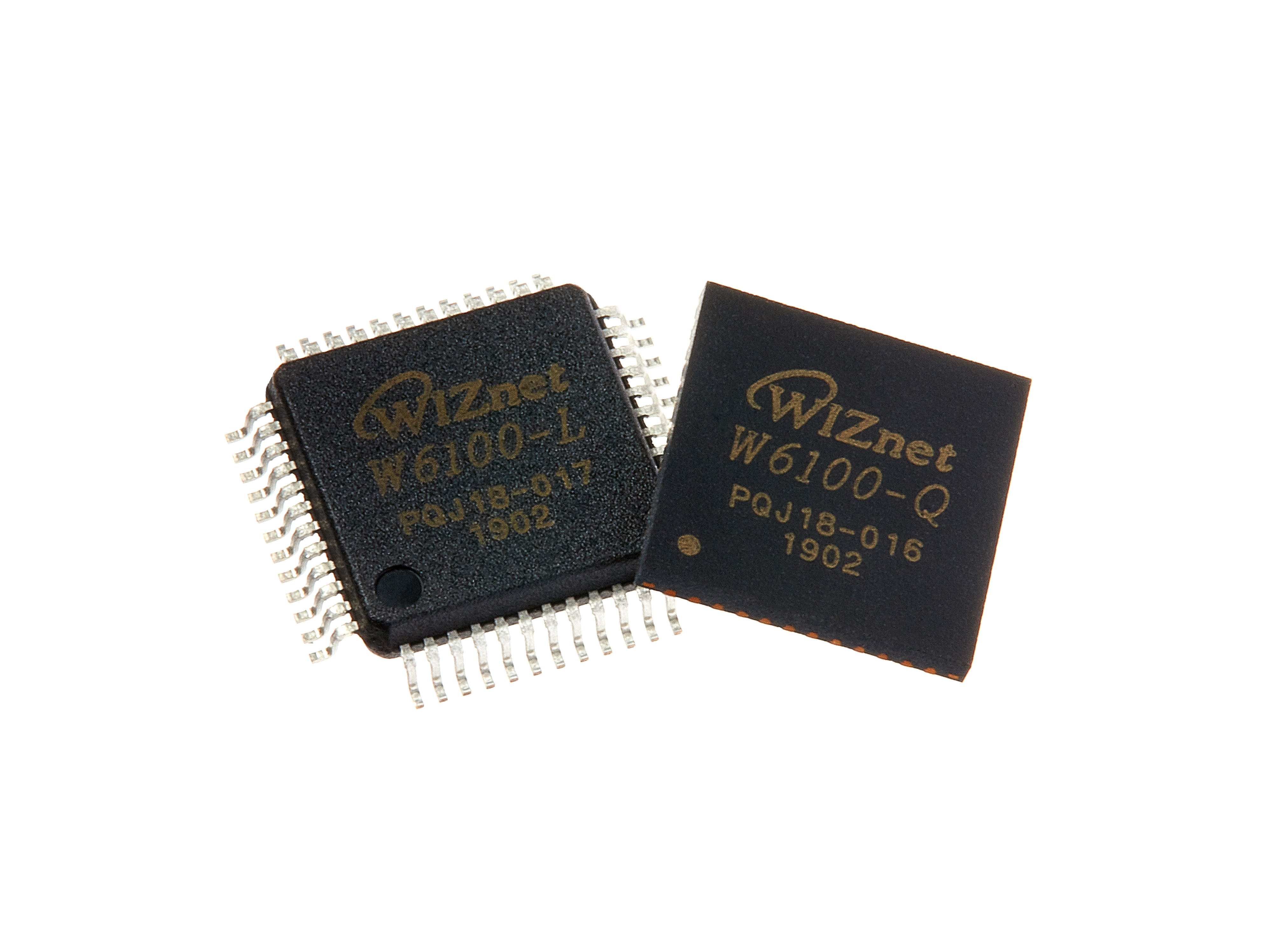

- W6100 (Wired Ethernet): Parallel Bus Integration and High-Speed Data Reliability

The decisive reason for adopting the W6100 as the system's main network interface is its support for an 8-bit Parallel Bus. The W6100 connects directly to the Motorola 68k processor's classic Memory-mapped I/O structure, enabling seamless data exchange without any intermediate conversion processes. Furthermore, its Hardwired TCP/IP technology completely offloads both IPv4 and IPv6 protocol processing within the chip itself. This guarantees the 'connection reliability' essential for transferring large ROM files or source code in retro environments. As a result, the main CPU is entirely freed from complex network computations, allowing it to focus 100% on core system control.

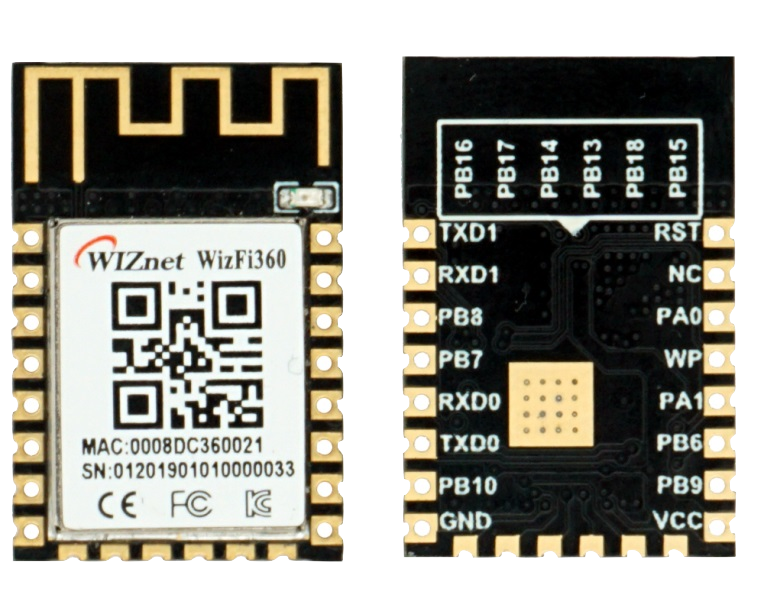

- WizFi360 (Wireless Wi-Fi): Development Convenience for Lightweight OS and Spatial Freedom

Since the A2560Me is a compact board designed for desktop use, wireless support is essential for environments with limited LAN cable access. The WizFi360 comes with a built-in TCP/IP stack and provides an AT command interface based on UART communication. This allows developers to quickly and easily implement wireless internet using only short commands, even in environments like EmuTOS where porting complex wireless LAN drivers is highly difficult.

WIZnet Chipset / Module Role Comparison

| W6100(Wired Ethernet Controller) | WizFi360 (Wireless Wi-Fi Module) | |

|---|---|---|

| Medium | Wired (high reliability) | Wireless (spatial flexibility) |

| Interface | 8-bit Parallel Bus | UART (serial) |

| Integration | Directly connected to the CPU's memory-mapped I/O for high-speed data transfer without protocol conversion | Connected independently from the main bus; handles lightweight control communications (e.g., system status reporting) |

| Protocol Processing | IPv4/IPv6 dual-stack hardware TCP/IP — zero CPU overhead | Built-in TCP/IP stack; accesses wireless networks via simple AT commands without complex drivers |

| System Role | Primary data communication requiring high bandwidth and reliability — e.g., transferring large ROM files or source code | Immediate internet access where LAN is unavailable; easy to integrate during early development |

The W6100 (parallel bus) handles heavy, reliability-critical main communications, while the WizFi360 (serial) covers development convenience and external control — maximizing hardware resource efficiency through clear role separation.

4. System Operation Flow

The system operates on a strictly divided, modular architecture.

- External communication — Wired and wireless packets arrive from outside the system.

- Hardware offloading (WIZnet) — The W6100 and WizFi360 handle initial parsing of complex protocols (IPv6, TCP, etc.) entirely in hardware.

- Payload transfer — Only the processed, clean payload data is passed to the internal system over the parallel or serial bus.

- Main compute focus — The MC68LC060 (CPU) and Kintex-7 (FPGA) can dedicate 100% of their compute resources to multimedia (VICKY graphics, retro audio) and core application processing, without network interruption.

5. Industrial Scalability

The A2560Me's hardware architecture extends beyond a hobbyist device and serves as a relevant technical reference for B2B industrial applications.

- Smart retrofitting for industrial legacy equipment — Many industrial environments still rely on production equipment driven by 8-bit/16-bit MCUs. When connecting these machines to smart factory networks, the parallel bus-based hardware TCP/IP integration demonstrated by the A2560Me is a direct reference. Engineers can implement fast, stable network connectivity without replacing existing main controllers.

- Open-source ecosystem and flexible design — The modular design supporting various I/O configurations on a single board is well-suited for customized requirements. With global developers actively porting EmuTOS, FUZIX, and similar software, there are abundant development references and a stable validation environment for engineers evaluating WIZnet solutions.

6. Tech Stack Summary

| Category | Specifications |

|---|---|

| Main CPU | Motorola MC68LC060RC66 (32-bit legacy architecture) |

| FPGA / Logic | Xilinx Kintex-7 (VICKY graphics & retro audio core) |

| Wired Network | WIZnet W6100 (IPv4/IPv6 hardware TCP/IP, 8-bit parallel interface) |

| Wireless Network | WIZnet WizFi360 (Wi-Fi module, AT command-based UART interface) |

| Memory | 1 GB DDR3, 8 MB SRAM, 4 MB Flash |

| Expansion & I/O | PCIe Gen 2 (4-lane), USB OTG, SD card, legacy I/O (DB9, PS/2, etc.) |

| Target OS | EmuTOS, FUZIX, OS-9 |

FAQ

Q. Does the W6100 require a software TCP/IP stack on the host side? No. The W6100 processes IPv4/IPv6, TCP, UDP, and ICMP entirely in hardware. The host CPU only reads and writes to socket registers via memory-mapped I/O — it never handles raw packet data. This is what makes it viable on a 66 MHz 68k processor.

Q. How is the WizFi360 controlled from the 68k CPU? The WizFi360 is connected over UART and controlled entirely via AT commands. No dedicated driver or OS-level network stack is needed. Any code that can write to a UART register can send AT commands to the module.

Q. Which operating systems currently run on the A2560Me? As of early 2026, EmuTOS is actively being ported to the platform. FUZIX and OS-9 are listed as planned targets but are not yet available. The community-maintained FoenixMCP kernel supports earlier Foenix models; A2560Me support is not yet confirmed.

Q. Can this architecture be applied to other legacy MCU-based industrial systems? The core pattern — connecting a W6100 via parallel bus to offload TCP/IP from a low-MHz processor — is not specific to the 68k. Any MCU or CPU with a parallel bus and memory-mapped I/O can use the same approach. The W6100 also supports SPI mode, which extends compatibility to systems without a parallel bus interface.

https://linuxgizmos.com/foenix-labs-a2560me-brings-mc68lc060-cpu-fpga-graphics-and-pcie-expansion/